基于JTAG的星型扫描接口的设计及其仿真

4 星型扫描技术接口的设计及验证

在本文中,星型扫描技术接口是基于JTAG接口,根据硬件升级层次化的方法进行设计,并利用FPGA硬件平台进行设计和QuartusⅡ软件进行仿真验证。此接口的特点是在原有的TAP.1接口上添加了支持星型扫描技术的功能,此功能中最为关键的技术是技术分支的选择和串型等价扫描。下面重点对它们进行设计验证。

4.1 技术分支选择的设计及验证

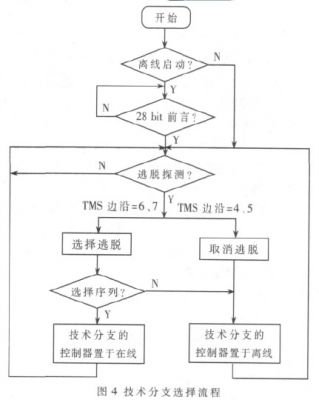

选择与取消逃脱的探测和一串选择序列完成技术分支的选择操作。TAP.7控制器通过扫描拓扑训练识别不同分支所在的位置。一旦训练完成,每一技术分支呈现出单独的技术特性,提供技术分支选择的基础。在选择序列中包含了选择技术分支的信息TOPOL寄存器值,不同的技术分支类型具有不同的TOPOL寄存器值。只有技术分支被选择,它才能被操作。技术分支选择的流程设计如图4所示。

下面分别就长型选择序列和短型选择序列对技术分支选择功能进行仿真验证, 其验证仿真结果如图5所示。

4.2 串型等价扫描的设计及验证

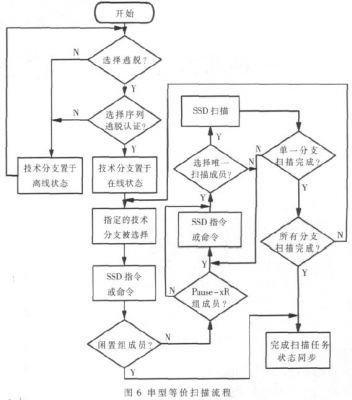

在星型拓扑扫描技术中,提供了一种串型等价扫描的方法,这样既完成了星型扫描功能,又实现了TDO数据的驱动冲突保护。其具体设计过程为:

(1)选择所有的分支;

(2)选择所有分支中的所有CLTAP,并指明标准协议的应用;

(3)选择单一的技术分支,并将状态推进至Run-Test/Idle状态;

(4)使用SSD指令选择技术分支中不参与串型等价扫描的STL,使它们成为闲置组成员(其余的 STL 为扫描组成员);

(5)推进扫描组中的STL的CLTAPC状态移入Pause-xR 状态;

(6)使用SSD来识别一个扫描目标的STL,并对目标STL进行移位扫描,再回到Pause-xR状态,但不经过Update-xR状态,使其他不是闲置组成员的STL成为Pause-xR组成员(这使得被SSD识别的STL成为扫描组唯一的成员);

(7)对技术分支中不是闲置组成员的每一个STL重复步骤(6);

(8)待技术分支中所有非闲置组成员完成扫描移位后,选择技术分支中非闲置组的CLTAPC经过Update-xR状态,并最终回到Pause-xR状态,中间不经过Shift-xR 状态;

(9)重复步骤(6)、(7),完成整个单一技术分支的扫描;

(10)重复步骤(3)至(9),完成所有技术分支的扫描;

(11)将所有的CLTAPC状态同步到ADTAPC的状态,完成串型等价扫描的整个过程。

串型等价扫描的设计流程如图6所示。

串型等价扫描的关键是SSD操作,本文中,以单个TAP.7控制器和CLTAPC为例,对SSD指令的功能仿真验证,结果分别如图7所示。

边界扫描测试技术广泛应用于超大规模集成电路中,测试标准的发展为测试接口设计提出了更高的要求。IEEE 1149.7测试标准中规范的TAP.7接口具有传统TAP.1接口所没有的功能特性,因此对它的研究具有深远意义。本文中设计的支持星型扫描技术的接口是一种基于原有JTAG器件的TAP.1接口,在TAP.1接口上添加相应的逻辑硬件层实现扩展功能的升级接口,在目前基于TAP.1接口的系统级测试中有很好的应用前景。本文中的接口设计方法具有良好的可扩展特性,为以后进一步功能升级奠定基础,从而避免了重复开发所带来的资源浪费,同时对IEEE 1149.7标准规范的系统器件的研究和设计具有很好的参考价值。

- 基于MC9328MX1嵌入式最小系统的设计(11-19)

- ARM硬件设计三:JTAG引脚和PIO引脚(02-27)

- Spartan-3 FPGA 的3.3V 配置(07-27)

- 32位ARM嵌入式处理器的调试技术(03-12)

- ARM嵌入式系统的在系统编程方案设计(06-07)

- JTAG仿真口电路设计(10-19)