基于JTAG的星型扫描接口的设计及其仿真

边界扫描测试技术飞速发展,测试与调试功能不断增强,硬件IP模块向集成多个内核方向发展,以往芯片中传统的测试访问端口(TAP)中嵌入单一的测试访问端口控制器(TAPC)逐渐被系统芯片中嵌入多个TAPC所取代。为使单芯片中集成多TAPC的操作规范标准化,2009年提出的新的测试标准IEEE 1149.7。为解决系统集成复杂度越来越高所带来的测试调试任务困难,标准规范了一种支持星型扫描功能的IEEE 1149.7测试访问端口(在本文中称为TAP.7接口),其接口在原有的IEEE1149.1端口(JTAG)器件的基础上提供新的功能与特征[1]。目前,大量的集成系统和芯片接口都为IEEE 1149.1标准规范测试访问端口(TAP.1接口),既满足复杂系统测试的需要,又避免了重复开发所带来的浪费,最大化地重复利用目前已有的IEEE 1149.1 IP,基于原有JTAG器件的星型扫描技术的研究非常有应用价值和市场需求,本文针对支持星型扫描功能的接口进行研究、设计及验证。

1 IEEE 1149.7标准简介

IEEE 1149.7标准以IEEE 1149.1-2001边界扫描标准为基础,保持与之兼容的同时还增加新特性以支持测试与调试的扩展功能。标准规范了新特性的IEEE 1149.7测试访问端口(在本文中称为TAP.7接口)结构和控制时序逻辑,与IEEE 1149.1标准规范测试访问端口(TAP.1接口)所不同的是芯片中可嵌入多个测试存取端口控制器(TAPC),并给它们划分等级。标准中规范的TAPC等级由高到低包括:ADTAPC、CLTAPC和EMTAPC,它们在接口中成串型连接,且高等级的TAPC控制和管理低等级的TAPC。在功能特性方面:TAP.7接口定义了T0~T5 6个功能层次,每一层向上体现升级特性,向下体现兼容特性。T0层在启动时提供与TAP.1接口所规定的操作行为;T1层主要增加了电源控制功能;T2层增加了芯片级旁路功能,同时提供一种"热连接保护"作用;T3层增加了支持4-线星型拓扑扫描的机制;T4层提供了支持2-引脚连接方式的功能特性; T5层增加数据传输功能以及支持边界扫描以外的其他功能。

2 基于JTAG的TAP.7接口的升级特性

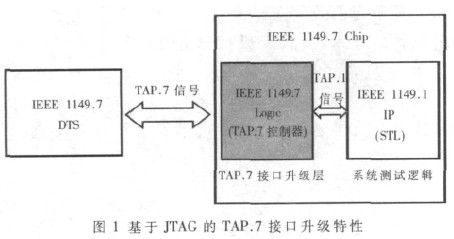

IEEE 1149.7测试标准定义了一种以IEEE 1149.1测试标准为基础的调试及测试系统(DTS)与目标系统(TS)之间的连接。此连接表现为:在IEEE 1149.1标准规范测试访问端口[2](在本文中简称TAP.1接口)上添加一个由IEEE 1149.7标准规范的标准控制逻辑来实现新的功能特性(在本文中称添加层为TAP.7控制器)。TAP.7控制器主要为IEEE 1149.7标准规范的测试调试信号与IEEE 1149.1标准规范IP的TAP.1接口提供兼容的测试调试接口(本文中简称TAP.7接口),这样可在原有TAP.1接口上对调试与测试新功能升级,其TAP.7接口升级特性的测试连接框图如图1所示。

如图1所示,TAP.7接口升级层中TAP控制器为ADTAPC(在本文中简称为TAPC),主要完成对TAP.7信号的控制操作,从而实现新的升级功能特性,并将TAP.7信号的测试与调试逻辑解码为符合TAP.1接口的时序信号,从而完成对IEEE 1149.1器件TAPC的控制。IEEE 1149.1 IP也可认为是具有符合IEEE 1149.1测试标准的测试JTAG口的器件[3] (在本文中以后简称为STL),其中包含的TAP控制器(在本文中统称为芯片级TAPC即CLTAPC)是完全符合IEEE 1149.1测试标准规范的TAP接口,主要完成器件的测试与调试逻辑的控制,从而完成相应的测试与调试任务。

3 星型扫描技术接口的原理及设计

完整的TAP.7接口升级层包括RSU、APU、EPU。RSU(复位选择单元)提供复位操作和TAP.7控制器选择取消操作。EPU(扩展协议单元)主要为T1-T3层 TAP.7接口提供了一个IEEE 1149.1 接口。APU为T4-T5层提供窄式(2-引脚)或宽式(4-引脚)TAP.7接口,为高级协议操作提供硬件支撑。根据实际功能的设计需求,TAP.7控制器可以由RSU、EPU和APU 中的任意组合构成,为TAP.7信号与STL的TAP.1接口之间提供了一座桥梁,且RSU、APU和EPU层并不影响STL扫描路径的长度。

3.1 星型扫描功能接口硬件设计

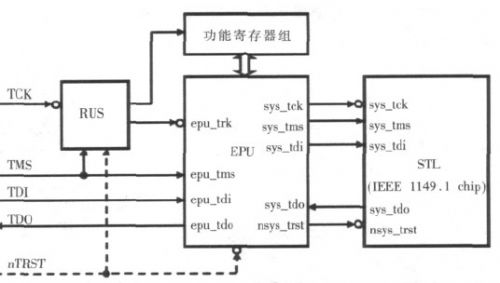

4-线星型扫描拓扑功能是TAP.7接口T0~T3层所定义的,组成星型拓扑的技术分支是广义的,可包括:TAP.7接口串型拓扑的技术分支、4线星型拓扑的技术分支、TAP.1接口的串型技术分支和其他的技术分支。本文主要是对前两种技术分支共享DTS连接的扫描功能进行研究。根据TAP.7功能扩展性和硬件层次性,星型扫描功能的TAP.7接口硬件层主要包括:RUS和EPU单元。其硬件设计原理框图如图2所示。

图2中,RSU单元层主要实现TAP.7控制器的在线或离线状态的控制操作,可以将不必要进行测试调试的控制器置于离线状态,大大优化了测试调试操作。在星型扫描拓扑或多种扫描拓扑技术分支共享DTS操作时, RSU单元提供了选择不同技术分支和控制器的功能。EPU单元的功能是将TAP.7信号解码成符合IEEE 1149.1标准规范的TAP.1信号,实现对CLTAPC的控制和完成STL的调试测试任务。

3.2 星型扫描技术接口设计原理

星型扫描的应用,可以优化扫描链的长度,它是并行的连接方式,因此在TAP可以灵活地添加或移出测试系统(比如:插卡式构架)中,星型扫描拓扑是很有效的。支持星型扫描的TAP.7接口具备以下功能:(1)支持星型扫描拓扑中的寻址能力。(2)JTAG接口中的TDO数据的驱动冲突保护。(3)在多技术分支共享DTS的操作中,提供选择不同技术分支的操作。下面对这些功能的原理进行详细介绍。

3.2.1 TAPC停泊状态

TAPC等级制度中存在一个称为"parking"(停泊)的TAPC 状态,当某一等级TAPC的状态处于停泊时,其高等级TAPC可操作,而该等级以及低等级TAPC不能操作,它的状态不随高等级TAPC的操作同步改变。某一等级TAPC控制的扫描链不作用时,TAPC的状态就可以停泊。选择与取消用来描述在任何等级中TAPC的扫描与停泊状态。支持星型扫描功能的TAP.7接口有TAP.7控制器的ADTAPC和STL的CLTAPC两个TAPC等级,其ADTAPC可以在任何状态下停泊,CLTAPC 状态可停泊的状态包括Test-Logic-Reset、Run-Test/Idle和Pause-XR状态。本文中取消与选择的设计,用门限时钟信号来达到对ADTAPC与CLTAC的选择与取消操作。

3.2.2 选择与取消

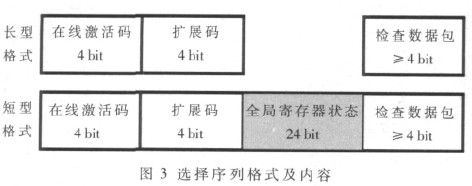

在IEEE 1149.7标准规范中,选择与取消功能的实现方法一般包括取消选择逃脱和取消选择警报。在本文中主要设计和验证了逃脱的操作。逃脱(Escapes)就是在1 bit周期内,不改变正常的信息交换情况下,将控制信息加载到正常传输的TCK(C)与TMS(C)信号上。TAP.7控制器探测TCK为逻辑"1"时TMS边沿的数目值从而作为逃脱产生的条件。当边沿数为4或5时,产生一个取消逃脱,使控制器离线;当边沿数为6或7时,产生一个选择逃脱,告知随之而来的是一串选择序列[4],如符合选择序列标准,将选择此控制器或控制器所在的技术分支并将它们置于在线状态,反之将置于离线。选择序列部分包括:技术相关部分与技术无关部分。其中技术无关部分指定要被选择的技术分支,技术相关部分响应在线申请和初始化在线设备。选择序列具体功能及格式如图3所示。

3.2.3 CID分配

在传统的串型扫描拓扑中,TAP控制器在串型扫描链中与DTS的相对位置提供了直接寻址能力,使用星型拓扑时,串型扫描拓扑提供的寻址能力消失了,因为TAP控制器在扫描链中具有相同的相对位置。控制器地址(TCA)可由IEEE 1149.1 器件的识别码(27 bit)与节点识别码(8 bit)组成。在实际应用中,TS中的TAP数一般很少,这样35 bit的TCA显得开销过大。从而,可利用一条TAP.7命令[5]CIDA分配一个4 bit的控制器识别码(CID)给TAP.7控制器,也可利用一条TAP.7命令CIDD取消控制器的CID。DTS可动态地分配CID到不同的TAP.7控制器,因此16个CID可被大于16的TAP.7控制器使用。

3.2.4 SSD

扫描选择指令(SSD)添加到TAP.7 控制器功能中用以提供一种在Pause-xR 或 Run-Test/Idle 状态停泊CLTAPC 的方式,它可防止星型扫描拓扑的TDO数据驱动冲突并提供与串型拓扑等价的扫描性能。SSD有三种类型:SSD_DA取消所有的CLTAPC;SSD_SA选择所有的CLTAPC;SSD_SOT或 SSD_SOC,根据TCA或CID选择目标CLTAPC。SSD_SOT与SSD_SOC 指令在不同的ADTAPC状态下有不同的操作:在Run-Test/Idle状态下, SSD传递的CID 或 TCA 与某一TAP.7控制器的CID或TCA匹配时,将选择这一TAP.7控制器的CLTAPC,但不对其他CLTAPC进行操作;但在Pause-XR状态下,它将选择目标CLTAPC,同时取消非目标CLTAPC。SSD必须在SSDE寄存器激活并且扫描格式支持星型扫描的情况下才能激活使用,SSD使用TDI数据来同时选择与取消一个或多个CLTAPC。

- 基于MC9328MX1嵌入式最小系统的设计(11-19)

- ARM硬件设计三:JTAG引脚和PIO引脚(02-27)

- Spartan-3 FPGA 的3.3V 配置(07-27)

- 32位ARM嵌入式处理器的调试技术(03-12)

- ARM嵌入式系统的在系统编程方案设计(06-07)

- JTAG仿真口电路设计(10-19)