AEMB软核处理器的SoC系统验证平台

SoC芯片的规模一般远大于普通的ASIC,同时深亚微米工艺带来的设计困难等使得SoC设计的复杂度大大提高。仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80%,采用先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如基于Nios II微处理器的SOPC系统与基于MicroBlaze微处理器的SOPC系统等。它们功能强大,而且配有相应的开发环境与系统集成的IP核。但每个器件厂商的SOPC系统只适用于自己开发的器件,同时需要支付相应的使用费用且没有源代码,所以在学习以及普通设计开发验证中使用起来会有诸多的不便。

本文采用OpenCores组织所发布的32位微处理器AEMB作为SoC系统的控制中心,通过Wishbone总线互联规范将OpenCores组织发布维护的相关IP核集成在目标SoC系统上,构成了最终的SoC验证平台。

1 AEMB及Wishbone总线介绍

AEMB是一款高效的开源微处理器软核,在指令上与Xilinx公司针对其器件开发的Microblaze微处理器兼容,而且在结构上还有所增强。它主要有以下特点:

①软核设计得非常小,相对于其他的一些微处理器软核,在物理实现上占用较少的硬件逻辑资源;

②支持硬件上的多线程,可以有效地执行操作系统相关的代码;

③AEMB是在LGPL3下开发的,所以它完全可以作为一个部分嵌入到一个大的设计中,同时非常适合一些科研院所以及高校或者个人用来学习;

④支持Wishbone总线规范,可以非常容易地集成其他的一些支持Wishbone总线规范的开源IP核;

⑤完全通过一些参数来定义系统的可配置功能,如系统的地址空间和一些其他可选的功能单元;

⑥在指令上99%与EDK6.2兼容,可以方便地使用已经非常成熟的开发工具链。

Wishbone总线规范是一种片上系统IP核互连体系结构。它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度。Wishbone总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容目前存在的所有综合工具,可以用多种硬件描述语言来实现。Wishbone总线提供了4种不同的IP核互连方式:

◆点到点(point-to-point),用于两IP核直接互连;

◆数据流(data flow),用于多个串行IP核之间的数据并发传输;

◆共享总线(shared bus),多个IP核共享一条总线;

◆交叉开关(crossbar switch),同时连接多个主从部件,可提高系统吞吐量。

2 SoC系统验证平台总体框架

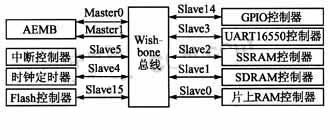

SoC系统中主要包含的IP模块有:32位开源微处理器软核AEMB、中断控制器、时钟定时器、Wishbone总线、片上RAM控制器、SDRAM控制器、SSRAM控制器、Flash控制器、UART16550控制器、GPIO控制器。整个SoC系统的总体结构如图1所示。

图1 SoC系统总体结构

为了方便后续开发与应用,本SoC系统中的Wishbone总线仲裁采用了开源的IP软核wb_conmax。其为8×16的结构,即在该Wishbone总线模块中可以使用8个主设备与16个从设备。本系统中使用了8个从设备接口和2个主设备接口。AEMB软核中没有提供时钟定时器与中断控制器,为了正常使用该软核,本系统中加入了中断控制器和时钟定时器,这两个控制器是作为从设备添加进来的。针对一些对存储空间需求很少的应用,系统将片上RAM作为主存储器。然而,FPGA片上存储器的空间是非常有限的,为了能够运行需要大量存储空间的操作系统,以及让系统正常上电启动,就需要外部存储器作为系统的主存储器。所以,系统中还添加了SDRAM、SSRAM控制器及Flash存储器。UART16550控制器和GPIO控制器作为2个从设备连接在系统中。

3 SoC系统验证平台具体构建

3.1 AEMB版本的选择与配置

AEMB软核采用最新的EDK62版本。本设计的目的在于整个SoC系统验证平台的构建,对微处理器性能及整个SoC系统的具体应用性能没有要求。为了简化设计,将AEMB软核中可配置的一些优化选项全部禁掉。这样不仅省去了对FPGA硬件逻辑资源的占用,而且也避免了因一些具体细节使用不当而带来的诸多问题。

3.2 片上RAM的生成

为了减少对FPGA逻辑资源的占用,同时又能够满足最基本的启动代码的存放与运行,将片内存储器的大小设为4 KB。使用Altera公司的FPGA开发环境QuartusII 9.0中的MegaWizard Plug-In Manager工具,来生成设定大小为4 KB的片上RAM。EDA开发工具生成的片上存储文件仅是具有相关存储器地址、数据及读写控制信号的一个HDL描述文件。为了能够在本SoC系统中使用,需要将其包装成符合Wishbone总线接口的一个从设备,以挂接在系统的Wishbone总线上。

3.3 片外存储控制器的配置

在该SoC系统上,片外存储控制器主要有SDRAM、Flash、SSRAM控制器。根据台湾友晶公司的DE2-70开发板上实际存储芯片的需要,对控制器的数据总线宽度与地址总线宽度作相应的修改与定制。一般情况下,SDRAM作为系统的主存储器,Flash用来存储系统的一些固化程序。在对一些实时系统进行时间参数测量的过程中,为了减小程序运行空间中时序的不稳定性影响,一般情况下测试程序都是在SSRAM器件中运行的。

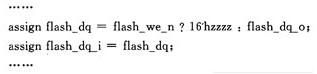

作为存储器件的物理芯片,数据总线的端口基本上都是双向的,而在片内系统中数据端口基本上都是单向的。这些片外存储控制器在进行物理板级的连接时需要对相应的数据端口作处理。以Flash控制器为例,数据总线的双向I/O口具体实现RTL代码如下:

其他的存储器(如SDRAM、SSRAM)的数据总线双向I/O的实现,也都是采用这种方法来完成的。

3.4 中断控制器与时钟定时器的配置

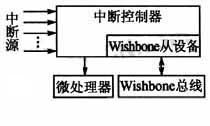

中断控制器主要用于接收外部中断源的中断请求,并对中断请求进行处理后再向CPU发出中断请求,等待CPU响应中断并进行处理。在CPU响应中断的过程中,中断控制器仍然负责管理外部中断源的中断请求,从而实现中断的嵌套与禁止。在本设计中,中断控制器的逻辑结构如图2所示。所采用的中断控制器主要负责接收片内IP核及片外器件所发出的中断请求,然后根据一定的优先级与规则将中断发送给微处理器。微处理器可以通过设置与读取相应的中断寄存器来管理查看中断优先级与中断状态。

图2 终端控制器逻辑结构

时钟定时器主要是作为操作系统的时钟滴答定时器,本质上就是一个简单的计数器。在每个系统时钟来到时计数器会自动加1,当计数器的值达到设定数值时便产生1次时钟中断。PTC是OpenCores组织发布的一个支持Wishbone总线接口的脉冲定时计数器。其不仅可以作为时钟定时器,还可以通过配置寄存器的设置产生PWM脉冲输出。本SoC系统中主要是使用PTC的定时器功能。

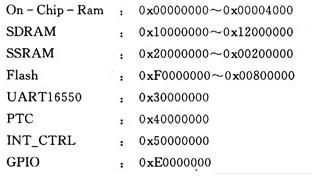

3.5 地址空间的分配

根据DE2-70开发板上各器件的特点与AEMB微处理器的中断例外向量表及wb_conmax的逻辑实现,系统地址空间分配结果为:

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)