SoC前段(ARM)嵌入式系统开发实作训练(下)

指令执行

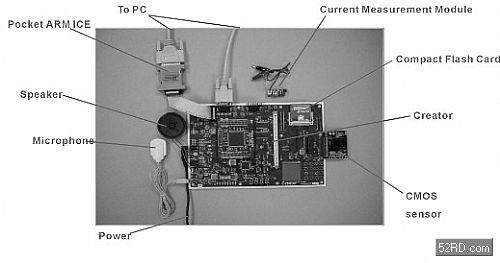

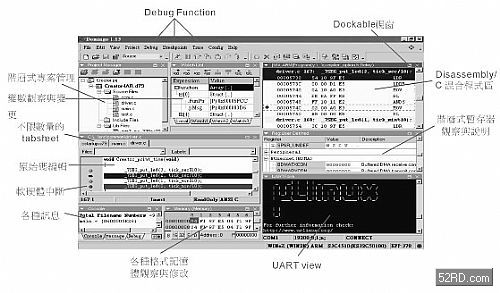

在RISC的精简指令中,它含有多种意义,因此较难理解。但在Debugger对CPU掌握的全透明下,就可清清楚楚看到指令的执行, 也加深对CPU的了解。为了观看指令与组合语言的执行,我们来开一视窗共解说它各处视窗的意义。首先要把ICE与Creator接上,并执行Domingo程式如图1图2。

图1 Pocket ARM ICE 与Creator的接线图

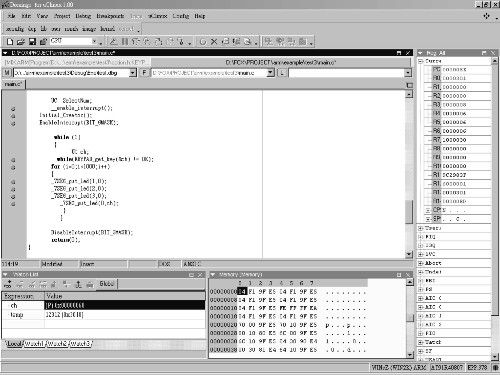

图2 Domingo IDE视窗画面

Example

在command下键入以下指令,以便等一下观看其各指令执行结果。虽然不甚了解指令,但在执行后,视窗会显示有变更(红色值)的资讯,您就会体悟原来如此。

STMIAR0,{R1-R5}

执行这个指令后,会将R1~R5等暂存器之内涵值储存到R0暂存器所指的记忆体位址。

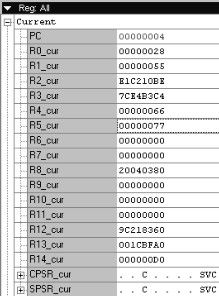

暂存器值

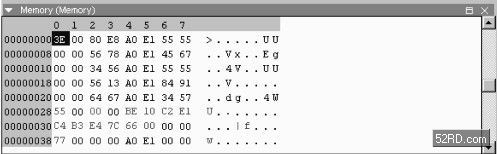

记忆体变化

程式执行

以keypad与7-seg为例,在project中去download一现成的程式来观看其执行,并在keypad上按键,而观看7-seg的变化。看了以后,发觉它并不陌生,与8051也差不多,只是惊讶Domingo操作环境比早期的ICE有着天壤之别的人机操作介面。

操作介面

上图中主要程式内容如下:

int main(void)

{

__enable_interrupt();

Initial_Creator();

EnableInterrupt(BIT_GMASK);

while (1)

{

UC ch;

while(KEYPAD_get_key(&ch) != OK);

for (i=0;i<1000;i++)

{

_7SEG_put_led(1,0);

_7SEG_put_led(2,0);

_7SEG_put_led(3,0);

_7SEG_put_led(0,ch);

}

}

DisableInterrupt(BIT_GMASK);

return(0);

}

在利用debug/load module载入已经compiler完成之程式后,执行free go便可测试程式之正确性并且进行debug。

程式建立与Compile流程

1.建立project

建立专案以管理您的相关程式并可将自订的工作环境储存起来。

2.Edit

开启Editor以编辑新建立的程式或开启一个已建立的程式。当然,这可以是Assembly或C语言的程式。

3.Compile

Domingo IDE支援外部的Compiler程式,透过一些简单的设定步骤,您可以直接在这个整合式的介面中执行compile与link来build您的project,也可以用make的方式只针对变更处build以增快速度。若您在compile的过程中发现了错误,还可以直接在错误讯息处double click以快速地直接跳至发生误错的原始码位置方便您的除错。

4.ICE的连接

当然除了硬体的接线外,还需要在Domingo中执行connect以与ICE正确地连接起来,此时目标板的控制权才会交给ICE。

5.Download

将compile完毕的程式档download至目标板的RAM区,Domingo支援多种格式的除错档,因此即便是没有整在Domingo介面中的外部除错档也可以下载下来哦。

6.Debug

在Domingo强而有力的除错功能支援下,相信这不会是一个太大的难题,不过却是一个最重要的部份,没有好工具的支援,这里将会是您整个开发专案中最费时的一个部份。

7.烧录

程式完成了,如有需要再配合一些记忆体位置的修改后就可以透过ICE直接烧录至ROM里面了。

8.独立测试

好啦,ICE的任务完成了!这时您已经可以将ICE与目标板脱离让系统板独立运作了,测试一下,是不是成功了呢?整个流程与以前8位元8051的做法似乎大同小异,但其实内里却又大有文章,想进阶至32位元开发的您,如果没有一个好的Debugger与ICE将会困难重重。

系统管理

这是32bit ARM CPU与8051截然不同的地方,一个单独的CPU core是不能动的,它要加上一些外围週边资源才能动起来,例如放程式的ROM区、放资料的RAM区、BUS连接的方式、cache/buffer的情况。这些资源要设定好,才能启动CPU执行指令。以下做一些描述:

一个包含了ARM core的微控制器皆会架构一个系统管理者(System Manager)来管理系统所提供的所有週边资源,其主要的功能有以下几种:

˙仲裁週边之优先权:由于ARM微控制器所提供的週边功能很多,故会发生多个週边同时要求进行存取的情况,这时系统管理者便会依据控制器内固定的优先权顺序,仲裁数个週边的系统匯流排存取要求。

˙记忆体所需的控制信号:提供存取记忆体时,所需的记忆体控制信号。例如:DMA控制器或CPU产生了一个相对应到DRAM bank的位址时,系统管理者的DRAM控制器会产生所需的标准/EDO存取信号或者是SDRAM存取信号。

˙I/O所需的控制信号:提供ROM/SRAM或者外部I/O bank之间匯流排传输所需的信号。

˙内/外部匯流排宽度差异之补偿:补偿外部记忆体匯流排和内部资料匯流排之间,不同匯流排宽度之资料流。

而针对系统记忆体管理部分,各个memory bank的位置、大小皆由current bank base pointer和current bank end pointer之设定所决定。故我们可利用base bank pointer/next bank pointer的概念去建立一个连续的记忆体应对。这个概念也就是将next bank的base pointer设定为与current bank的end pointer相同的位址。但是有一点必需注意的,就是这些连续位址不可有重叠的地方。

在可定址的空间范围里,各种bank的起始位址并不是固定的,我们可以利用系统暂存器去组态一个bank起始位址为bank的基底指标,而这个位址的解析度为64K byte,故bank的起始位址会定义为"基底指标左移16位元",而bank的结束位址为"下一个指标左移16位元的位址值减1"。

然而在power-on或reset之后,控制所有bank的adress pointer暂存器皆会初始化为预设值;在这个情况下,除了ROM bank0的next pointer以外的所有bank pointer皆会被设定为0。这也就是说,除了ROM bank0以外所有的bank,在系统启动后,皆会成为未定义状态。

ROM bank0的next pointer和base pointer在重置后分别会为0x200和0x000。这代表系统在重置后会自动定义ROM bank0的起始位址由0开始,并且总共拥有32Mbyte的空间,其算法如下:

base point = 0x000

next point = 0x200

故ROM bank0的位址范围为0x000 0000 ~ 0x1ff ffff(32Mbyte)

其计算的方式为:

起始位址 = 0x000左移16位元,故为0x000 0000

结束位址 = 0x200左移16位元-1,故为0x200 0000-0x1 = 0x1ff ffff

由于系统启动后,会由0x0的位址开始动作,故这个ROM bank0的初始定义就是为了使系统可以控制使用者所提供贮存在外部ROM的boot code,以使系统可以正确的启动。boot code的动作内容会依照使用者所需求的规划来撰写,一般会做系统初始化的工作以及依据实际上的外部记忆体应用和周边装置组态重新配置系统记忆体map。

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)