SoC前段(ARM)嵌入式系统开发实作训练(下)

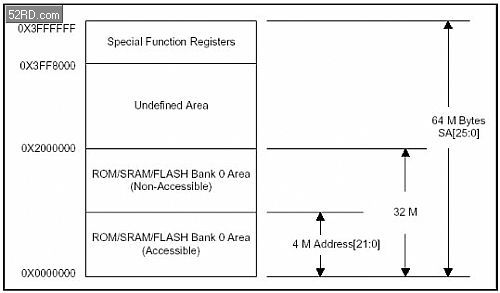

图3 重置后的系统记忆体map

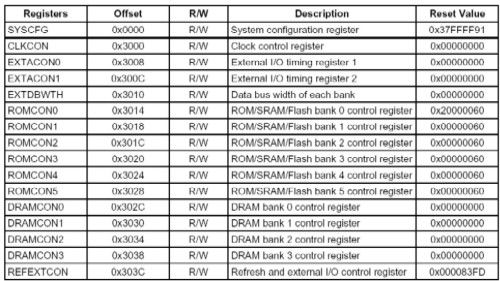

为了控制週边功能以及记忆体的操作,系统管理者使用一些专用的特殊暂存器集(如表1所示)来进行控制和管理。经由规划这些特殊暂存器之内含值,可以说明下列事情:

˙记忆体类型

˙外部匯流排宽度存取週期

˙控制信号时序(例如RAS和CAS)

˙memory bank位置

˙memory bank的大小可在随意的位址空间去使用

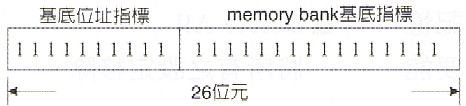

每个memory bank base pointer的位址解析度皆为64Kbyte(共16位元),而base address pointer为10bit,故整个可定址的记忆体空间为16Mword=64Mbyte(如表2所示)。

表1 系统管理者暂存器

表2 基本的memory bank位址组成

PCM

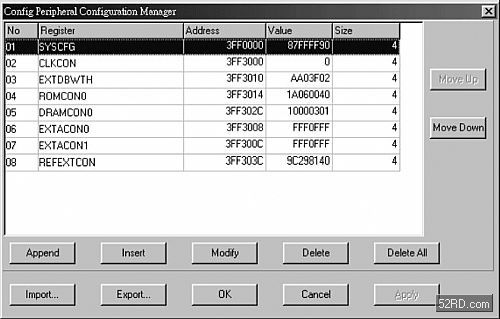

在Domingo中PCM就是在设定此一系统功能,因每个人所设计的硬体都不同,如未在PCM中设定正确,那Domingo对程式指令的存取就无法正确动,就像您在coding程式,在一开始也要初始化这些相对应的值,CPU才能正确的动作。

以ARM为基底的Embedded System,其记忆体系统(尤其是DARM)要能使用之前,通常要经过一连串的设定动作,而使用者如果每次使用ICE在下载程式到记忆体之前都要手动地去执行上述初始化记忆体工作的话,实在是一件很辛苦的事。而PCM命令则可为使用者代为执行上述例行之设定工作。

有以下二个方法可以开启PCM设定视窗

■使用configRconfig PCM.......命令

■使用configRHardware Options命令

进入Hardware Options设定视窗后再按Config PCM...按钮

图4 PCM视窗

以下说明PCM视窗内各按钮之功能

■Import

载入一个先前储存好的PCM档案

■Export

将目前PCM之设定存入指定之档案内。

■Move Up

将选定之设定列向上移动一列。

■Move Down

将选定之设定列向下移动一列。

■Delete

将选定之设定列移除。

■Delete All

将所有之设定移除。

■Modify

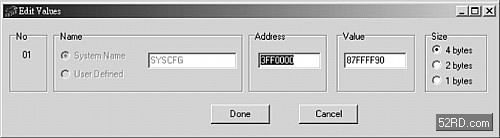

进行修改选定之设定列,并出现以下之设定视窗

图5 嵌入式系统架构

使用者可透过以上视窗来修改,名称、位址、设定值及资料长度等相位。完成后请按Done钮设定成修改好之工作。

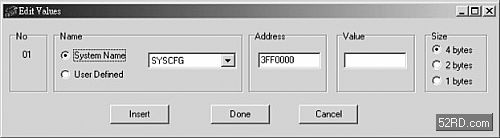

■Insert

将选定之设定列向下推,并在此插入一个设定列,此时会出现以下之设定视窗,供设定之用。

图6

在Name的栏位内如果要使用CPU内定的暂存器名称时,则可点选System Name并使用右侧下拉选单来选择一个已存在暂存器,在选择完毕后右侧的Address及Size栏位亦会被自动设定完成,你只需要输入Value项目即可。

若为自定名称的话,则请点选User Defined之后再依序输入Name、Address、Value及Size各栏位,最后按Insert即可。若要结束设定工作则按Done按钮。

■Append

同Insert命令,其差异在于Append是将新项目加入到最后的一设定列。

■Apply

利用此按钮可以将目前之设定项目立即对CPU及目标板做一次设定之工作。

Embedded Linux

有了CPU、指令与软体的技能后,再来就可建立系统概念,作业系统是一个学期的课程,不是在这里三言二语就可讲完,我们仅作重点说明。因是用现成Open Source的Linux程式,因此为了开发产品,产业界都只针对需自己需加入或修改的部份处理即可,也较快完成软体Porting,除非您是要透澈了解整个OS架构,也想自己创造一个OS,那就需深入各部份。因此Porting成功才是最重要的。

在这架构下就可清楚自己所要开发的是那一部份软体,只要针对它的相关界面了解,就可动手。因此如只开发AP S/W,那当然就不需进入到了解CPU的H/W,用Compiler、Debugger工具即可。但未来的产品,SoC嵌入式系统产品都不仅如此而已,它需与H/W连接,它不仅用到Compiler、Debugger,更需ICE的支援与其他硬体工具。因此如能建立对CPU与H/W的了解,未来的发展空间就更开阔,更有附加价值了。如图7所示,在Linux OS与H/W的中间那一层就是我们要去建立的能力。

图7

Device driver

这是在Linux下一个嵌入式系统产品必经之路,它依不同硬体而有不同之程式,但只要一个通,其他就容易了。因它与硬体有很密切关联性,我们已在Creator板上有些driver,在ICE与Domingo操作下,就容易了解它的过程了。因程式佔篇幅,就不在此描述。

FPGA之IP实作

FPGA上之IP开发、验証,这又是一学期的课程,在此我们也仅以重点式说明。在週边IP FPGA模组连接头上,可更换不同FPGA或CPLD模组(未来性)。在目前的Create Ph-FPGA-XC2S上,它的主要特点是:(一)可做基本组合逻辑与序向逻辑实作,(二)与ARM CPU程式紧密结合之逻辑设计,(三)软体或硬体最佳化选择之评估,(四)序列 ←→并列资料转换。

其他可发挥的硬体功能如下:

■FPGA:

XC2S30-5(30K gate counts)

■Codec:

˙16-Bit,26-KSPS

˙Built-in Microphone

■Analog To Digital:

8-Bit serial I/O ADC with 2 channel multiplexer

■SRAM:

128K×8Bit,12ns

■7 Segment LED×1

■9 LED Lamps

■4 Way DIP Switch

■1 Tag Switch

■1 DC Buzzer for tone generation

■PS2 Connector ×1 for PS2 keyboard or mouse

■Build in Xilinx download cable header circuit

我们仅以简单之解码功能做范例,但它需配合Xilinx ISE 4.1 以上工具来开发,再Download入板上。就可由CPU执行程式去驱动逻辑IP,在LED上看到显示的结果,以培养系统化思考,创作的能力。

【范例】:由ARM CPU送来的值经逻辑解码、Latch显示在LED上

--

-- MICROTIME COMPUTER INC.

--

library IEEE,synopsys;

use synopsys.attributes.all;

use IEEE.std_logic_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity TEST is

port (

GSR_IN : in STD_LOGIC;

IO_ADDR : in std_logic_vector(15 downto 0);

IO_DATA : inout std_logic_vector(15 downto 0);

nECS3 : in std_logic;

IO_nOE : in std_logic;

IO_nWE : in std_logic;

IO : inout std_logic_vector(9 downto 0);

LED : out std_logic_vector(7 downto 0)

);

end TEST;

architecture TEST of TEST is

signal GSR1, nGSR1 : std_logic;

signal PORT_READ : std_logic;

signal CS_PORT : std_logic;

signal sIO_nWE, sIO_nOE : std_logic;

signal FPGA_CTRL : std_logic_vector(7 downto 0);

begin

-- #####################################################################

-- #################### GSR

-- #####################################################################

GSR1 <= GSR_IN;

nGSR1 <= not GSR_IN;

-- #####################################################################

-- ##### DECODING

-- #####################################################################

CS_PORT <= ’1’ when(nECS3=’0’ and IO_ADDR(11 downto 8)=X"0") else ’0’;

PORT_READ <= ’1’ when(CS_PORT=’1’and sIO_nOE=’0’) else ’0’;

LED <= FPGA_CTRL;

IO_DATA <= "000000" & IO when(PORT_READ=’1’) else "ZZZZZZZZZZZZZZZZ";

-- #####################################################################

-- ##### IO PORT

-- #####################################################################

p_PORT_WR : process (GSR1, sIO_nWE)

begin

if(GSR1 = ’0’)then

FPGA_CTRL <= X"00";

elsif(rising_edge(sIO_nWE)) then

if(CS_PORT = ’1’) then

FPGA_CTRL <= IO_DATA(7 downto 0);

end if;

end if;

end process;

end TEST;

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)