利用 Virtex-5 FPGA 降低功耗

VirtexTM-5 系列产品的推出,使得 Xilinx 公司再一次成为向 FPGA|0">FPGA 客户提供新技术和能力的主导力量。过渡至 65 纳米工艺的 FPGA 具备采用更小尺寸工艺所带来的传统优势:低成本、高性能和更强的逻辑能力。尽管这些优势能够为高级系统设计带来激动人心的机会,但65纳米工艺节点本身也带来了新的挑战。

例如,在为产品选择 FPGA 时,功耗的考虑变得越来越重要。很可能下一代设计会需要在功耗预算不变(或更小)的情况下,集成更多的特性和实现更高的性能。

在本文中,我将分析功耗降低所带来的好处。还将介绍 Virtex-5 器件中所使用的多种技术和结构上的革新,它们能提供功耗最低的解决方案,并且不会在性能上有任何折扣。

降低功耗的好处

低功耗的 FPGA 设计所带来的优势不仅是能满足器件工作的散热要求。虽然满足元件指标对于性能和可靠性十分重要,但如何实现这一点对于系统成本和复杂性都有着巨大的影响。

首先,降低 FPGA 的功耗使你能够使用更便宜的电源,这样的电源使用的元件数量较少,并且占用的 PCB 面积也较小。高性能的电源系统的成本通常为每瓦0.5到1美元。低功耗的 FPGA 直接降低了系统的整体成本。

其次,由于功耗直接与散热相关,低功耗使你能够使用更简单、更便宜的热量管理解决方案。在很多情况下,设计者将不再需要散热器,或者只需要更小、更便宜的散热器。

最后,由于低功耗工作意味着更少的元件和更低的器件温度,因此将提高整个系统的可靠性。器件工作温度每降低10℃,就相当于元件寿命提高了两倍,因此对于需要高可靠性的系统而言,控制功耗和温度十分重要。

功耗:挑战和解决方案

FPGA (或任何半导体器件)中的总功耗等于静态功耗和动态功耗之和。静态功耗主要由晶体管的泄漏电流引起,即晶体管即使在逻辑上被关断时,从源极"泄漏"到漏极或通过栅氧"泄漏"的小电流。动态功耗是器件核心或 I/O 在开关过程中消耗的能量,与频率相关。

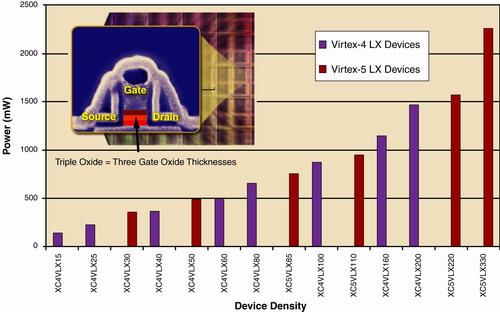

图1:85℃时的静态功耗比较 静态功耗 动态功耗 = CV2f 其中C是结点开关时的电容,V是电源电压,f是开关频率。65纳米工艺节点使 FPGA 的逻辑能力和性能比传统器件有了显著提高,也就是说更多的结点工作在更高的频率上。如果其它方面的条件不变,动态功耗将会增大。 |

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 利用Virtex-5 FPGA实现更高的性能(04-29)

- 实现多端口1Gbps 和10Gbps TCP/iSCSI 协议处理任务卸载解决方案(07-10)

- 一种基于FPGA的接口电路设计(11-18)

- 设计性能:物理综合与优化(04-28)