一种基于FPGA的接口电路设计

时间:11-18

来源:嵌入式研究

点击:

【摘 要】 在简要介绍了PC/AT键码、旋转开关和EPM7128结构特点的基础上,介绍了利用FPGA实现旋转开关信号到PC/AT键码转换的设计方法。

关键词:接口电路,FPGA,键码

在专用电路设计中,为了方便操作与控制,要对电路设计提出各种具体要求。本文即为一设计实例,其设计要求为:在旋转开关的控制下,产生所需的PC/AT键码控制信号,即当旋转开关左转时,每转动一个位置,产生一个左箭头键码和断开码(E0、6B、E0、F0、6B)信号,控制光标左移一个位置;旋转开关右转时,每转动一个位置,产生一个右箭头键码和断开码(E0、74、E0、F0、74)信号,控制光标右移一个位置;当按下一次旋转开关的接通按键时,产生一个回车键码和断开码(50、F0、50)信号,控制光标换行。为了实现这一设计要求,设计中采用Altera公司生产的可编程逻辑芯片EPM7128SLC,利用Maxplus2软件完成设计任务。

1 基本概念

1.1 旋转开关简介

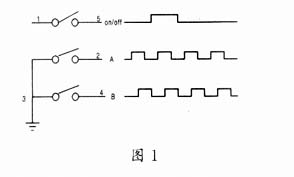

旋转开关由A、B两个通道开关、一个按压通断开关构成,当左右旋转时,A、B通道分别输出具有90度相位差的控制信号;当按下通断开关时,输出一个通断控制信号。旋转开关的构成及输出波形如图1所示。

1.2 PC/AT键码特点

PC/AT键码由接通码与断开码构成,当键按下时,产生相应的PC/AT键码,当键释放后,产生对应的断开码,不同的按键对应不同的键码和断开码,如左箭头的键码为E0、6B,断开码E0、F0、6B;右箭头的键码为E0、74,断开码E0、F0、74;回车键的键码为50,断开码为F0、50。每发送一个键码包含11个数据位,即1个起始位、8个数据位(低位在前,高位在后)、1个奇偶校验位、1个停止位;在键码传送的同时,还传送一个与键码同步的时钟信号,用于同步键码数据的接收;键码中每个数据位的传送发生在键码时钟的下降沿,时钟的波特率为16Kbps左右。

1.3 EPM7128简介

EPM7128是Altera公司生产的建立在多阵列结构基础上的高性能可编程逻辑器件,其内部具有符合IEEE1149.1标准的JTAG接口用于在线下载和修改程序,其内部具有2500个可使用门阵列、128个宏单元、8个逻辑阵列块,EPM7128SLC84具有68个用户可使用I/O接口。

2 软件设计

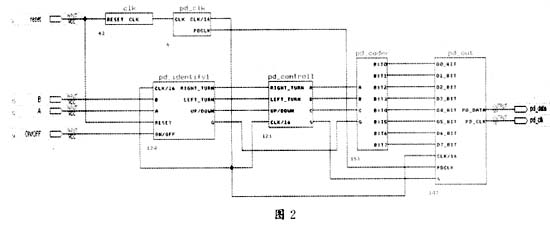

为了利用FPGA将旋转开关信号转换成PC/AT键码信号,所设计的FPGA软件由时钟发生器模块(clk)、时钟编码模块(pd_clk)、旋转开关状态识别模块(pd identify)、输出数据编码控制模块(pd_control)、码器模块(pd coder)、输出模块(pd out)构成,其功能连接如图2所示

时钟发生器模块的功能为:在reset信号的控制下,产生频率为15.5kHz的时钟信号,其振荡源为由5个非门构成的串联环路,该振荡器产生的振荡信号经分频电路分频,获得所需频率的振荡信号clk。

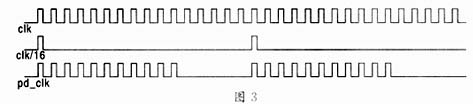

时钟编码模块的功能有两个,一是产生其它功能模块所需的基准控制信号clk/16;二是产生所需的PC/AT时钟信号pd clk,如图3所示。

旋转开关状态识别模块的功能是正确地识别旋转开关的状态,并产生相应的控制信号;如果旋转开关向左旋转一个位置,则输出一个Left turn识别信号;如果旋转开关向右旋转一个位置,则输出一个识别信号;如果按压一次旋转开关上的接通开关,则输出一个Up/Down识别信号。

输出编码控制模块和编码器模块的功能是在旋转开关识别信号的控制下,产生相应的输出编码控制信号,控制编码器,使编码器产生相应的编码信号;如果输入一个Left turn识别信号,则依次输出E0、6B、E0、F0、6B五个编码信号;如果输入一个 识别信号,则依次输出E0、74、E0、F0、 74五个编码信号;如果输入一个Up/Down识别信号,则依次输出50、F0、50三个编码信号。

输出模块的功能是:根据输入的编码信号,确定校验位的值,如编码信号中有奇数个1,则校验位为0,否则为1;根据输入的编码信号与生成的校验位,产生符合PC/AT键码格式要求的键码信号。

3 仿真结果

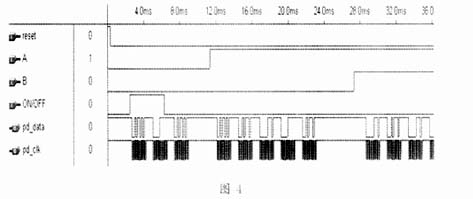

按照设计要求,利用Maxplus2软件进行功能设计与仿真,在完成模块功能设计与各功能模块仿真之后,进行整体功能模块连接与仿真,整体模块连接如图2所示,功能仿真结果如图4所示。其中,reset信号为复位信号,A、B、ON/OFF信号为来自旋转开关的输出信号,所设计的

FPGA输出的PC/AT键码时钟与数据信号分别为pd_clk和pd_data。

4 硬件结构

所设计的FPGA程序,通过JTAG口与旋转开关相连接的输入接口、用于输出PC/AT键码和时钟的输出端口。

关键词:接口电路,FPGA,键码

在专用电路设计中,为了方便操作与控制,要对电路设计提出各种具体要求。本文即为一设计实例,其设计要求为:在旋转开关的控制下,产生所需的PC/AT键码控制信号,即当旋转开关左转时,每转动一个位置,产生一个左箭头键码和断开码(E0、6B、E0、F0、6B)信号,控制光标左移一个位置;旋转开关右转时,每转动一个位置,产生一个右箭头键码和断开码(E0、74、E0、F0、74)信号,控制光标右移一个位置;当按下一次旋转开关的接通按键时,产生一个回车键码和断开码(50、F0、50)信号,控制光标换行。为了实现这一设计要求,设计中采用Altera公司生产的可编程逻辑芯片EPM7128SLC,利用Maxplus2软件完成设计任务。

1 基本概念

1.1 旋转开关简介

旋转开关由A、B两个通道开关、一个按压通断开关构成,当左右旋转时,A、B通道分别输出具有90度相位差的控制信号;当按下通断开关时,输出一个通断控制信号。旋转开关的构成及输出波形如图1所示。

1.2 PC/AT键码特点

PC/AT键码由接通码与断开码构成,当键按下时,产生相应的PC/AT键码,当键释放后,产生对应的断开码,不同的按键对应不同的键码和断开码,如左箭头的键码为E0、6B,断开码E0、F0、6B;右箭头的键码为E0、74,断开码E0、F0、74;回车键的键码为50,断开码为F0、50。每发送一个键码包含11个数据位,即1个起始位、8个数据位(低位在前,高位在后)、1个奇偶校验位、1个停止位;在键码传送的同时,还传送一个与键码同步的时钟信号,用于同步键码数据的接收;键码中每个数据位的传送发生在键码时钟的下降沿,时钟的波特率为16Kbps左右。

|

1.3 EPM7128简介

EPM7128是Altera公司生产的建立在多阵列结构基础上的高性能可编程逻辑器件,其内部具有符合IEEE1149.1标准的JTAG接口用于在线下载和修改程序,其内部具有2500个可使用门阵列、128个宏单元、8个逻辑阵列块,EPM7128SLC84具有68个用户可使用I/O接口。

2 软件设计

为了利用FPGA将旋转开关信号转换成PC/AT键码信号,所设计的FPGA软件由时钟发生器模块(clk)、时钟编码模块(pd_clk)、旋转开关状态识别模块(pd identify)、输出数据编码控制模块(pd_control)、码器模块(pd coder)、输出模块(pd out)构成,其功能连接如图2所示

|

时钟发生器模块的功能为:在reset信号的控制下,产生频率为15.5kHz的时钟信号,其振荡源为由5个非门构成的串联环路,该振荡器产生的振荡信号经分频电路分频,获得所需频率的振荡信号clk。

时钟编码模块的功能有两个,一是产生其它功能模块所需的基准控制信号clk/16;二是产生所需的PC/AT时钟信号pd clk,如图3所示。

旋转开关状态识别模块的功能是正确地识别旋转开关的状态,并产生相应的控制信号;如果旋转开关向左旋转一个位置,则输出一个Left turn识别信号;如果旋转开关向右旋转一个位置,则输出一个识别信号;如果按压一次旋转开关上的接通开关,则输出一个Up/Down识别信号。

输出编码控制模块和编码器模块的功能是在旋转开关识别信号的控制下,产生相应的输出编码控制信号,控制编码器,使编码器产生相应的编码信号;如果输入一个Left turn识别信号,则依次输出E0、6B、E0、F0、6B五个编码信号;如果输入一个 识别信号,则依次输出E0、74、E0、F0、 74五个编码信号;如果输入一个Up/Down识别信号,则依次输出50、F0、50三个编码信号。

输出模块的功能是:根据输入的编码信号,确定校验位的值,如编码信号中有奇数个1,则校验位为0,否则为1;根据输入的编码信号与生成的校验位,产生符合PC/AT键码格式要求的键码信号。

|

|

3 仿真结果

按照设计要求,利用Maxplus2软件进行功能设计与仿真,在完成模块功能设计与各功能模块仿真之后,进行整体功能模块连接与仿真,整体模块连接如图2所示,功能仿真结果如图4所示。其中,reset信号为复位信号,A、B、ON/OFF信号为来自旋转开关的输出信号,所设计的

FPGA输出的PC/AT键码时钟与数据信号分别为pd_clk和pd_data。

4 硬件结构

所设计的FPGA程序,通过JTAG口与旋转开关相连接的输入接口、用于输出PC/AT键码和时钟的输出端口。

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)

- FPGA协同处理的优势(04-29)