小间距LED屏:芯片端要让我满意,你得做到这几点

ESA距离、划道宽度、不同层的边界线间距等都有其限制,芯片的电流特性、SD工艺能力、光刻的加工能力决定了具体限制的范围。通常,P电极到芯片边缘的最小距离会限定在14μm以上。

其二是划裂加工能力的限制。SD划片+机械裂片工艺都有极限,芯片尺寸过小可能无法裂片。当晶圆片直径从2英寸增加到4英寸、或未来增加到6英寸时,划片裂片的难度是随之增加的,也就是说,可加工的芯片尺寸将随之增大。以4寸片为例,如果芯片短边长度小于90μm,长宽比大于1.5:1的,良率的损失将显著增加。

基于上述原因,笔者大胆预测,芯片尺寸缩小到17mil2后,芯片设计和工艺加工能力接近极限,基本再无缩小空间,除非芯片技术方案有大的突破。

2.亮度提升

亮度提升是芯片端永恒的主题。芯片厂通过外延程式优化提升内量子效应,通过芯片结构调整提升外量子效应。

不过,一方面芯片尺寸缩小必然导致发光区面积缩小,芯片亮度下降。另一方面,小间距显示屏的点间距缩小,对单芯片亮度需求有下降。两者之间是存在互补的关系,但要留有底线。目前芯片端为了降低成本,主要是在结构上做减法,这通常要付出亮度降低的代价,因此,如何权衡取舍是业者要注意的问题。

3.小电流下的一致性

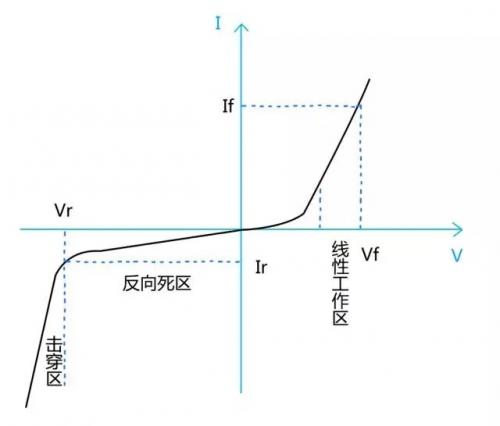

所谓的小电流,是相对常规户内、户外芯片试用的电流来说的。如下图所示的芯片I-V曲线,常规户内、户外芯片工作于线性工作区,电流较大。而小间距LED芯片需要工作于靠近0点的非线性工作区,电流偏小。

在非线性工作区,LED芯片受半导体开关阈值影响,芯片间的差异更明显。对大批量芯片进行亮度和波长的离散性的分析,容易看到非线性工作区的离散性远大于线性工作区。这是目前芯片端的固有挑战。

应对这个问题的办法首先是外延方向的优化,以降低线性工作区下限为主;其次是芯片分光上的优化,将不同特性芯片区分开来。

4.寄生电容一致性

目前芯片端没有条件直接测量芯片的电容特性。电容特性与常规测量项目之间的关系尚不明朗,有待业者去总结。芯片端优化的方向一是外延上调整,一是电性分档上的细化,但成本很高,不推荐。

5.可靠性

芯片端可靠性可以用芯片封装和老化过程中的各项参数来描述。但总的说来,芯片上屏以后的可靠性的影响因素,重点在ESD和IR两项。

ESD是指抗静电能力。据IC行业报道,50%以上芯片的失效与ESD有关。要提高芯片可靠性,必须提升ESD能力。但是,在相同外延片,相同芯片结构的条件下,芯片尺寸变小必然带来ESD能力的削弱。这是与电流密度和芯片电容特性直接相关的,无法抗拒。

IR是指反向漏电,通常是在固定反向电压下测量芯片的反向电流值。IR反映的是芯片内部缺陷的数量。IR值越大,则说明芯片内部缺陷越多。

要提升ESD能力和IR表现,必须在外延结构和芯片结构方面做出更多优化。在芯片分档时,通过严格的分档标准,可以有效的把ESD能力和IR表现较弱的芯片剔除掉,从而提升芯片上屏后的可靠性。

总结

综上,笔者分析了随着小间距LED显示屏的发展,LED芯片端面临的系列挑战,并逐一给出了改善方案或方向。

应该说,目前LED芯片的优化还有很大的空间。如何提升,还待业者发挥聪明才智,持续不断的努力。

- 技术让位于应用,小间距LED显示屏不破不立(08-24)

- 2016年,小间距LED不光要价格低(12-01)

- 2015的小间距LED风潮,2016还刮的起来吗?(01-04)

- 不做整体解决方案,小间距LED显示屏只有死路一条?(02-25)

- 这家公司在小间距LED业玩的风生水起(05-01)

- 要说本土技术有啥全球骄傲,中国LED封装算一号?(04-05)