DDR3T型等长设置

时间:10-02

整理:3721RD

点击:

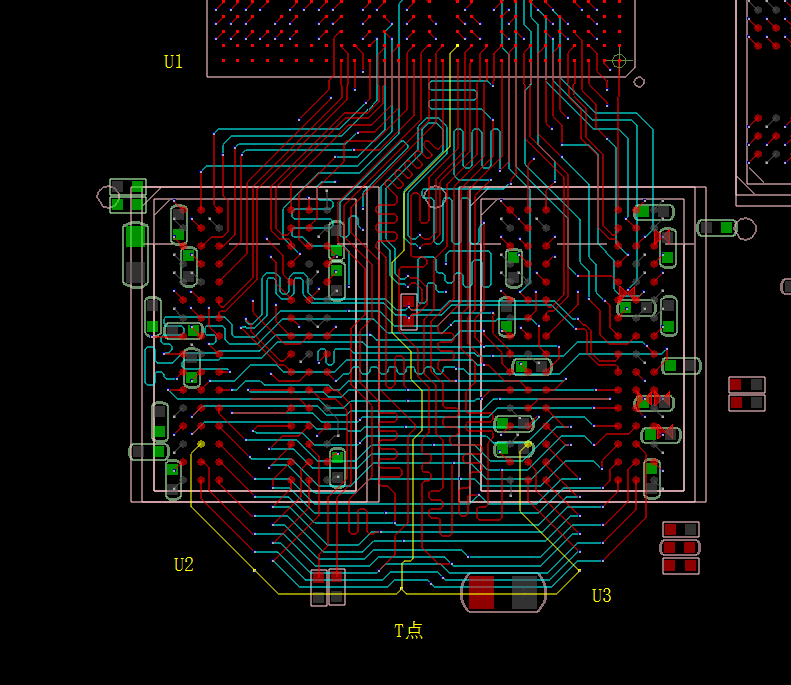

各位大神。如图,T型结构等长中,按照那种等长来走线比较合适?第一种:U1--T,T--U2,T--U3各个部分分别等长;第二种:U--T1+T--U2+T--U3各个部分相加等长.按照那种方法来走线比较合适?

怎么没有人了 难道说今天比较忙吗?

第一种属于较多的走法,做到分断等长 ;

就是说,你颗粒Fout 出来的,最好也做到等长,然后T部分做好等长 ,最后就可以在

规则哪里设好规则,绕主干道的线了,绕绿就好了

楼上正解,我们一般都是这么做的

DDR3是不是菊花链更好些

求解释

好久没走过DDR了。都不会走了估计!

三段对应等长对?主干道绕线指的是每段?还是?

三段对应等长 能保证整个NET等长 不见得吧

还是感觉第一种:U1--T,T--U2,T--U3各个部分分别等长 比较好

没有数据支撑 只是偶尔看到一些资料说的 DDR3速度比较快 而T型拓扑在T点处的反射比较大 眼图质量偏差希望有大神看到提供些理论支持 证实或反驳都好啊

这是DDR2的走法

有的DDR3支持延时补偿,就可以用fly-by。

没有延时补偿的,用T型结构。

DDR3是不是菊花链更好些