DDR3地址线与数据线相对长度有没有什么强制要求吗?

时间:10-02

整理:3721RD

点击:

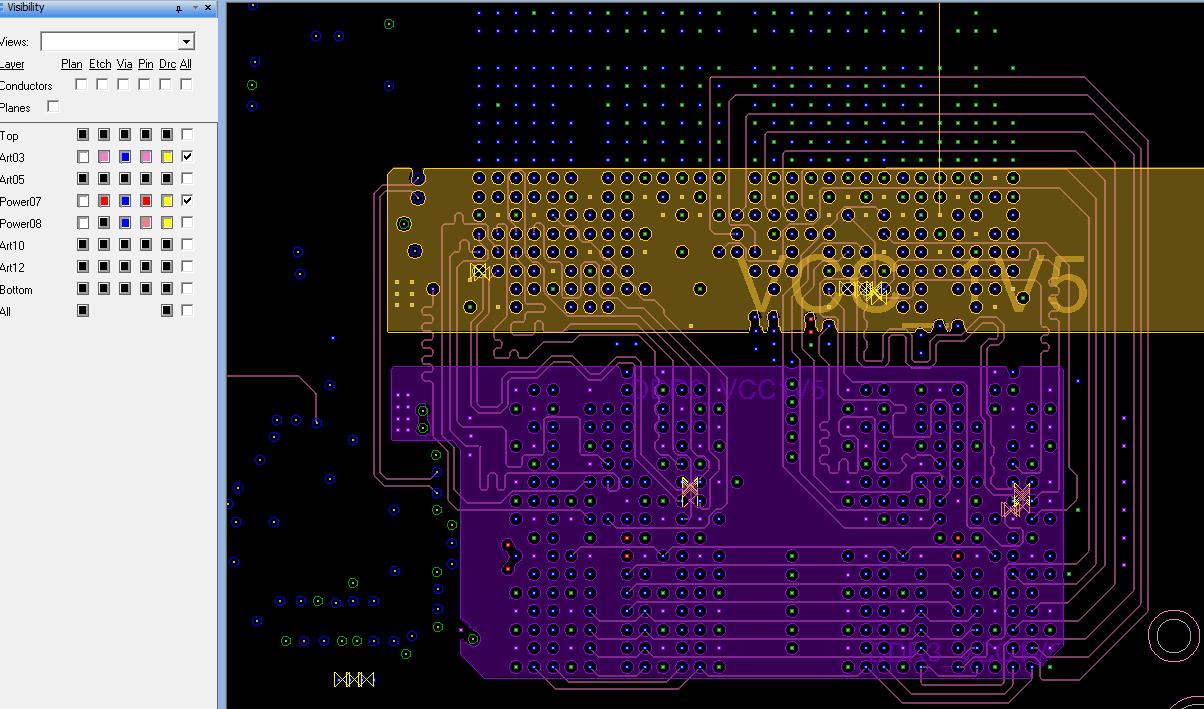

总觉得地址线太长了,DDR3地址线与数据线相对长度有没有什么强制要求吗?求解,谢谢.

弄清时钟的关系

没层了么!感觉这么走不太合适!地址线走到其他电源的参考平面了吧

没了,这是4颗DDR3,一面放2颗,布线空间很小.倒是有一个电源层可走,不过会跨电源分割平面,怎么弄呢?

没有任何要求。

DSP的1.5V与DDR3的1.5V之间串了个大的EMI电容,所以两个1.5V平面分开了,这样可以参考吗?

地址参考电源和地试试~~~

就是连个1.5v是分开的,可以参考吗?

你把地址类走线全部走在电源平面下面,但不要跨分割。

TKS.

另外,不一定要地址线上下两面都是电源,也可以是一个电源,一个地。

另外,不一定要地址线上下两面都是电源,也可以是一个电源,一个地。

电源都是1.5v,都是给DDR3供电的,应该可以合并成一个。DE SB.

你这种情况没碰到过!最好还是参考ddr供电电源所在的平面好点!

要不要严格限制长度,这要看你的产品速度要求。ddr3的信号线一定要参考本身的供电电源和地。