铺铜遇到的问题,求解

时间:10-02

整理:3721RD

点击:

为什么cadence我铺铜时,铜和过孔规则里设置的间距是6mil,为什么实际铺出来确是0mil,每次铺铜都报DRC错误,是我哪里设置的不对还是怎么回事,求大神帮帮忙,在此谢过!

规则没设置好

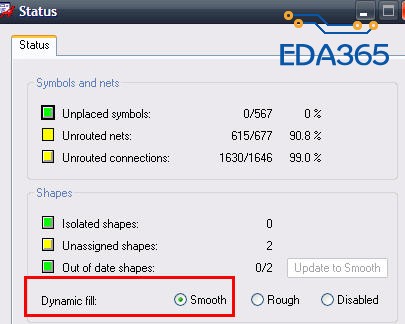

Display->Status下图中的选项设置了吗?

这里设置没问题,已经设置了,还是不行,请看一下图片。

updata to smooth

你这个是平面层, 设置成负片了没?在xsection里面设置的。

另外, 你的thermal relief或者ANTIPAD可能有问题。最后, 你这个应该是平面的负片层, 设置的6mil间距在这里不适应。从这里可以看出,你应该没设置成负片~~~

shap NET与链接的网络之间设置布线规则