我的6层FPGA板, 请大家指点.

时间:10-02

整理:3721RD

点击:

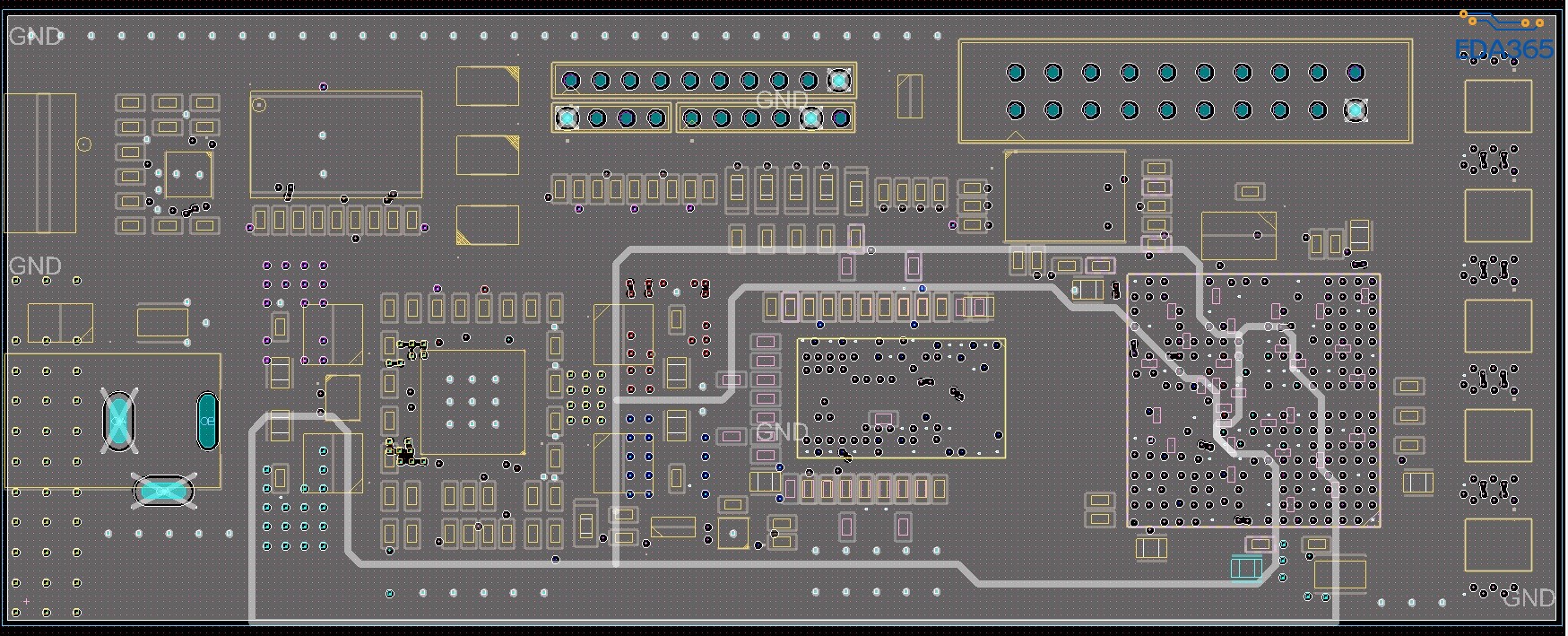

layer 01:

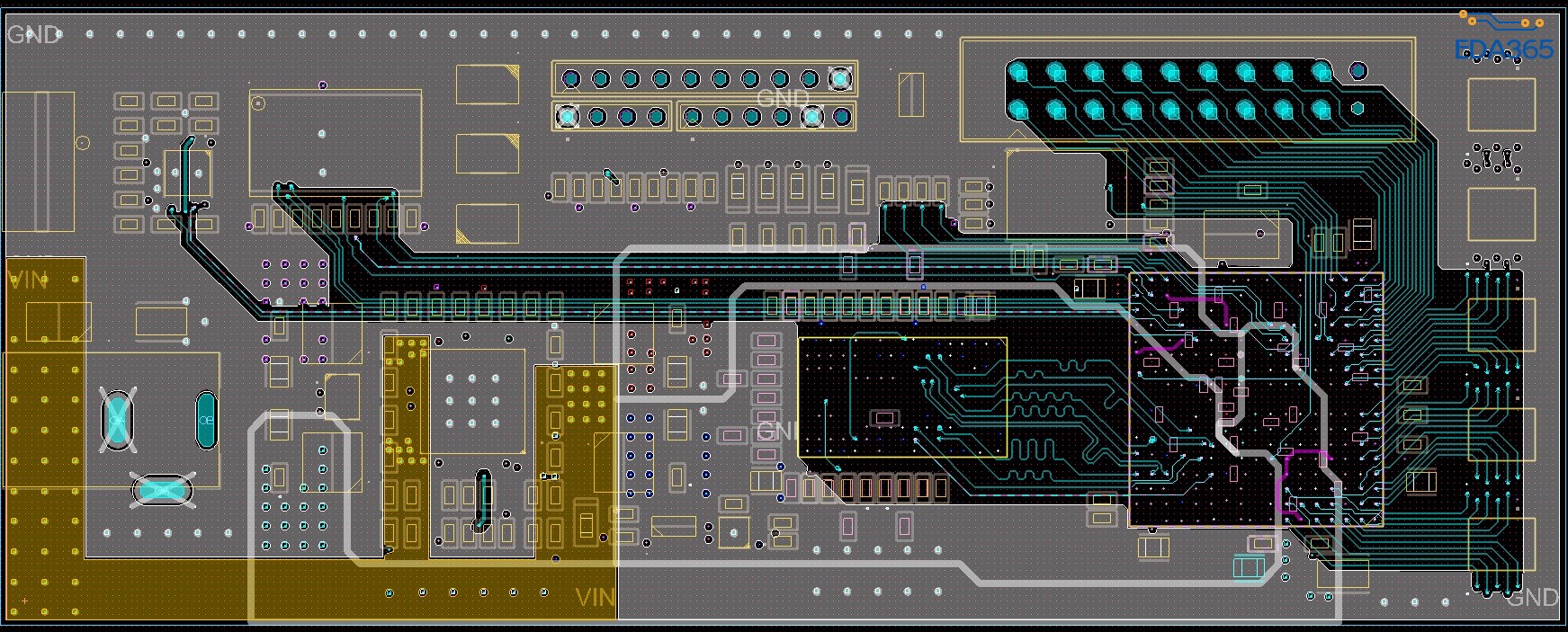

layer 02:

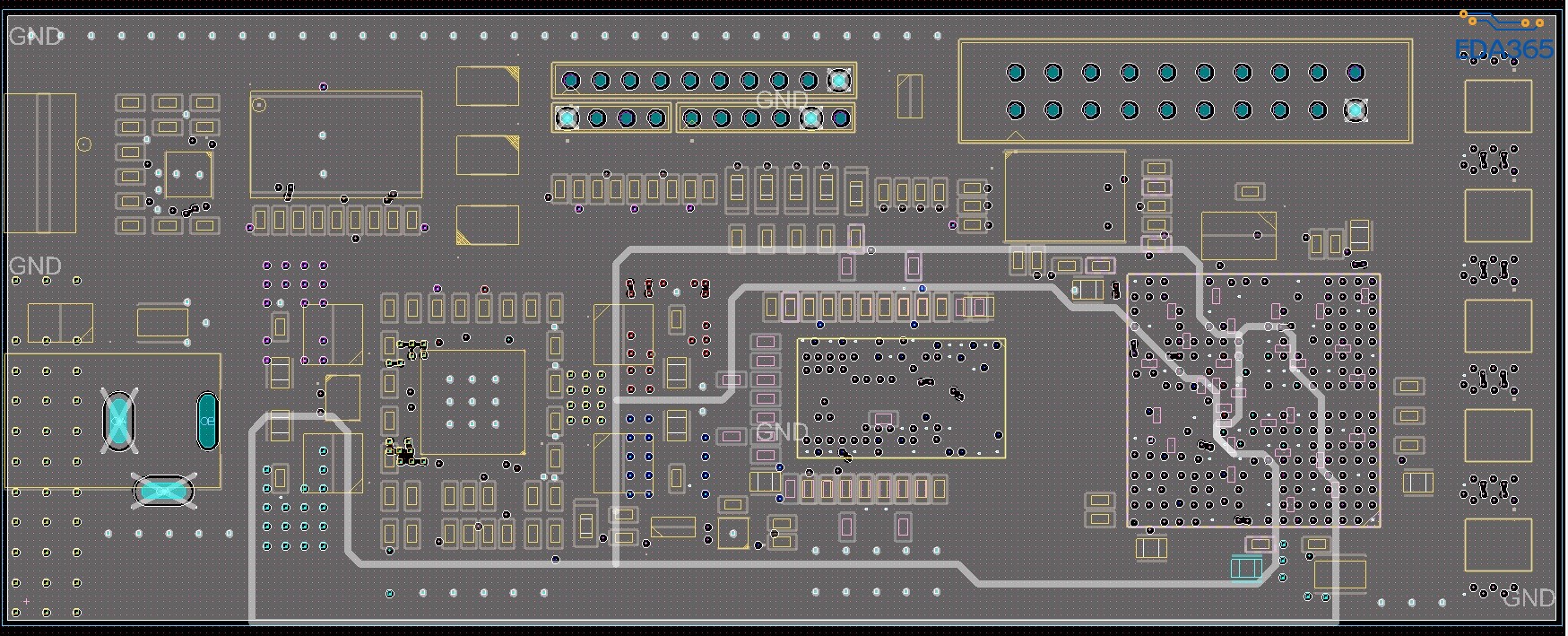

layer 03:

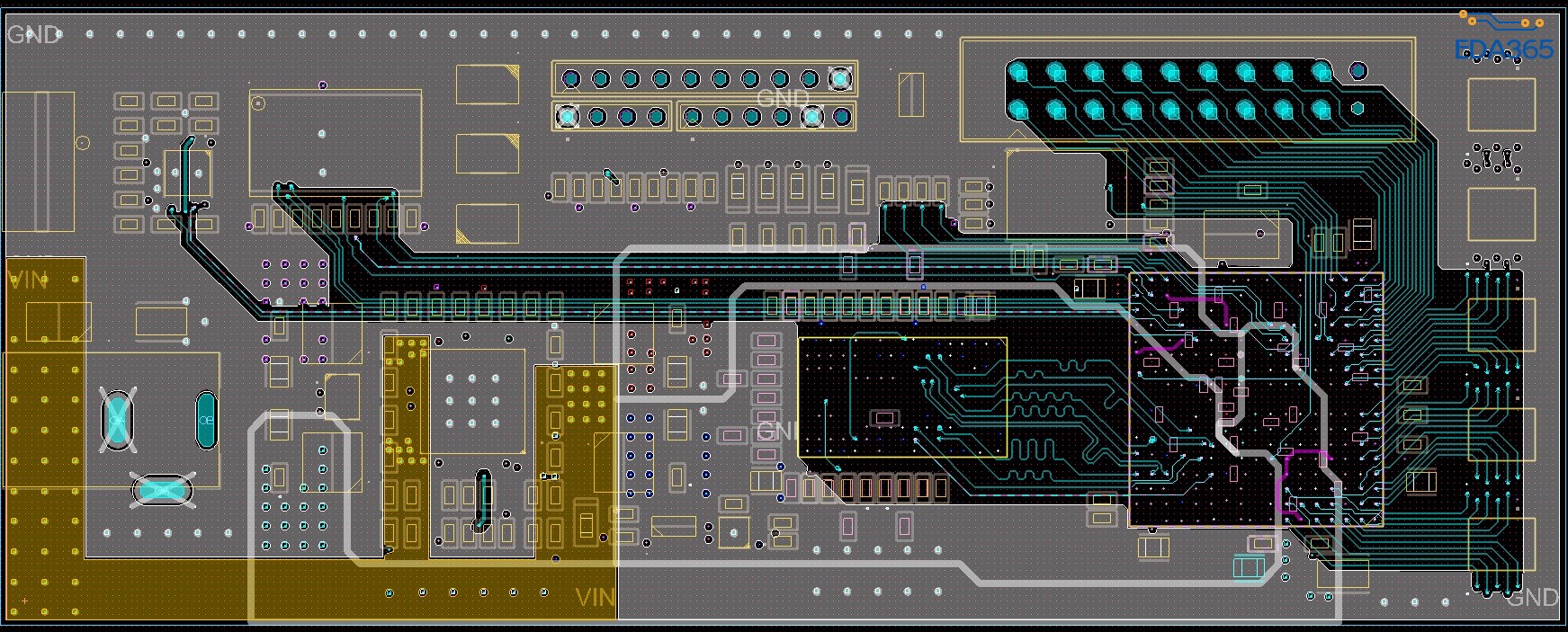

layer 04:

layer 05:

layer 06:

layer 02:

layer 03:

layer 04:

layer 05:

layer 06:

看着还不错!

画得很不错

比我画的好

brd放出来呗

画得挺好的

为什么不把第四层全部作为电源层,第五次全部作为地层?

建议fpga的核心电源(vcc_1v0)铜皮加宽,目前进bga区域的铜皮太窄了,并且走的比较远。

走个ddr用了4层线,这个对于专业的pcb来说还差点意思

小编不错!有钱途

修改了一下顶层和电源层的电源部分:

ddr走线都没有参考地,信号完整性会差一些。

参考自身的电源就可以

个人感觉横着放比较好走 线也会短点

建議你拆掉重走,疊構改成 TOP/L2GND/L3IN1/L4VCC_IN2/L5GND/BOT.

TOP/L3 Ref L2 , BOT/L4VCC_IN2 Ref L5GBD.

4层应该就能搞定.