关于DDR3布线等长的一个小问题

时间:10-02

整理:3721RD

点击:

hello,早上好各位大师。小弟一早过来继续研究DDR3布线的问题的时候,在手册里面看到这样一张图,突然有点困惑,也大致能明白是什么意思,但是还是想请教一下各位大师的意见,看看小弟的理解是不是对的。

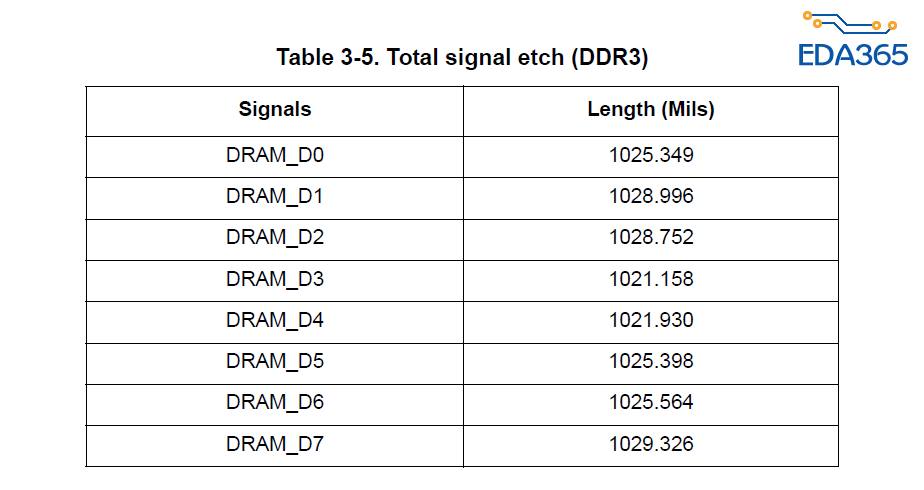

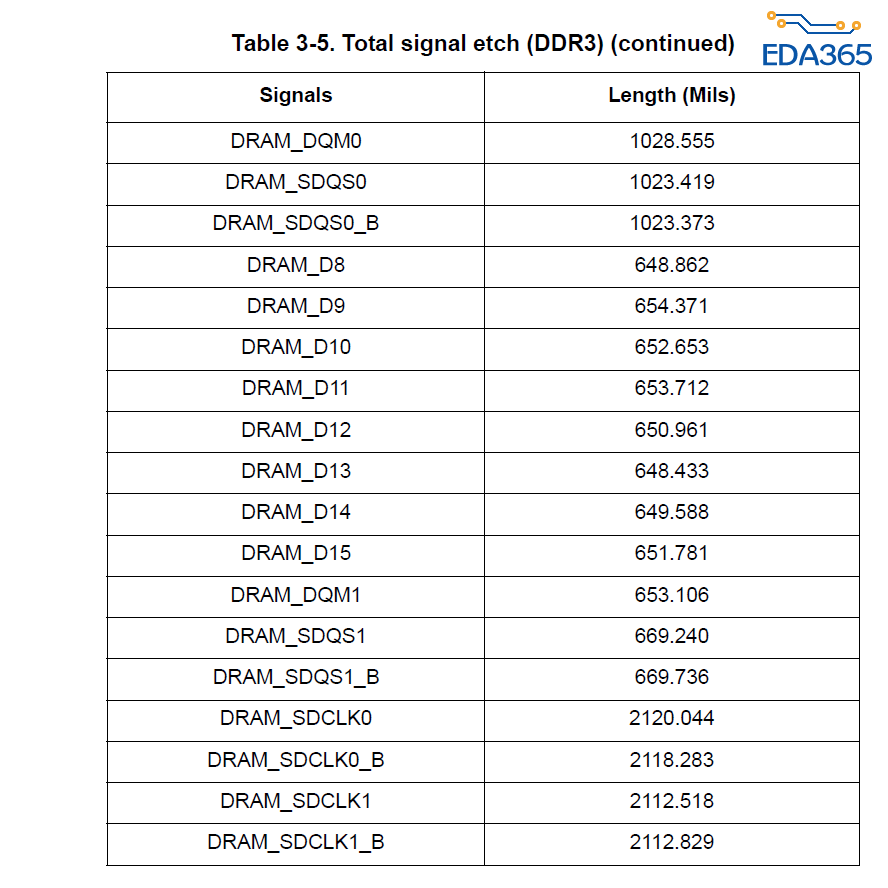

按照下面两幅图里面的表格,我简单的理解就是只要同分组的线等长即可,没必要一致要求所有分组的走线完全登场。那么问题又来啦,那么在多片DDR3的芯片上,是不是说不通芯片上的线也没有必要要求一致登场,只要CLK信号等长就可以了呢?我的意思也就是说,比如8个分组,byte0,byte1,byte2,byte3,byte4。那么也就是说只要byte0里面的先等长,byte1里面的线等长就可以了,不需要考虑所有的byte都要等长。最终所有DDR3芯片的CLK信号等长,就可以了呢?

按照下面两幅图里面的表格,我简单的理解就是只要同分组的线等长即可,没必要一致要求所有分组的走线完全登场。那么问题又来啦,那么在多片DDR3的芯片上,是不是说不通芯片上的线也没有必要要求一致登场,只要CLK信号等长就可以了呢?我的意思也就是说,比如8个分组,byte0,byte1,byte2,byte3,byte4。那么也就是说只要byte0里面的先等长,byte1里面的线等长就可以了,不需要考虑所有的byte都要等长。最终所有DDR3芯片的CLK信号等长,就可以了呢?

我的理解是这样:DDR等长围绕DDR 的clk信号为基准线展开,假如,地址线与CLK偏差一个范围值:+-200mil;DQS与CLK 偏差+-500mil;然DM、D0~D7是以DQS为基准线偏差;所以只要满足偏差值要求就可以,偏差值大,则每个字节长度偏差也大,反之,偏差值小,则看起来每个字节长度就都差不多

是的,如图里一样,数据组里,11根一组,组内等长即可。

不同的芯片对于DDR的等长是不一样的,你可以找到对应手册的layout建议手册看一下

曾经遇到一个海思的芯片,要求是不要做等长,按demo做,芯片内部已经做好了匹配

各组还是要参考信号线的时钟信号线长度,基本要保持一致,最大不超过600mil,也就是说,实际上布线的时候各组还是要求等长的。一般手册上都有说明的。

我基本也是这样认为的,数据线参考dqs等长,地址线参考CLK,dqs和CLK也是有长度要求,只是走线长度相差没那么严格

非常感谢大家的回复,我大致明白了,谢谢大家!

我下载的DDR手册都是引脚定义和时序,没有布局建议的啊

那个是数据手册,原理图用的

有的公司还会提供一个layout的手册

好的,我去找找,我都是镁光下载,找不到啊 +

小编,可以把DDR3手册资料发来学习一下吗

小编,D1这组和D9这组长度为什么相差这么大呢

不好意思,前一段时间在忙,就没上论坛,DDR3的资料大多都是在网上找的零零散散的东西。数据线差距很大,这个主要是应为他们在不同的组,只要保证每一组内等长就行了,不用保证每一组都等长。这个是DDR的特性,好像从DD2开始就支持这个了,你可以找找看。