天线处如何设计才能保证阻抗?

时间:10-02

整理:3721RD

点击:

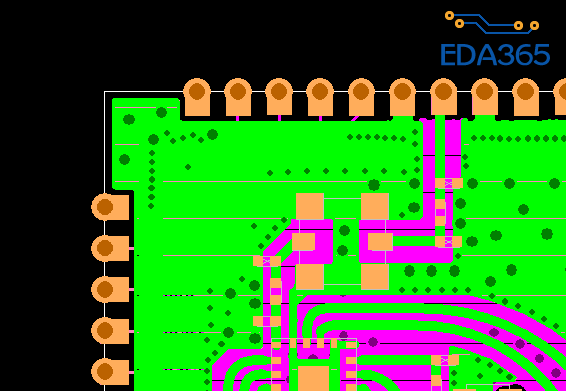

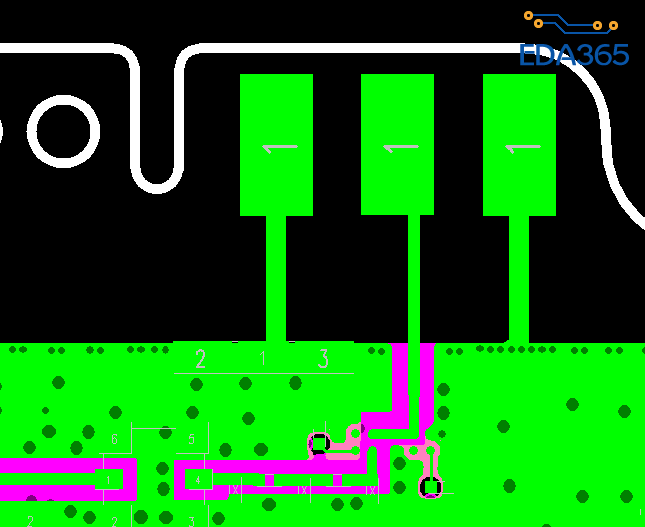

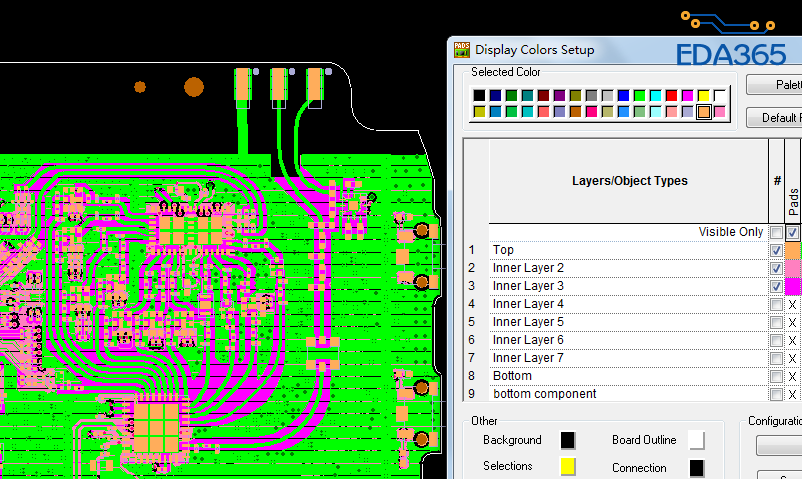

各位,如图,天线处如何设计才能保证阻抗? 天线处已净空了,没有平面参考(下部分有地参考,上部分净空处没地参考了),走线是不是要加粗啊,求支招?

我司暂时没见过射频座直接放板端禁空的情况。可能信号不好与没有参考层有关

看起来有点细

整条线宽是5mil, 板厂按50欧姆阻抗算出来的,关键净空后那一段要不要加粗?加粗到多少?

找手册说明吧...这种应该会给出参考方案的吧

没有啊,这种常规怎么处理?

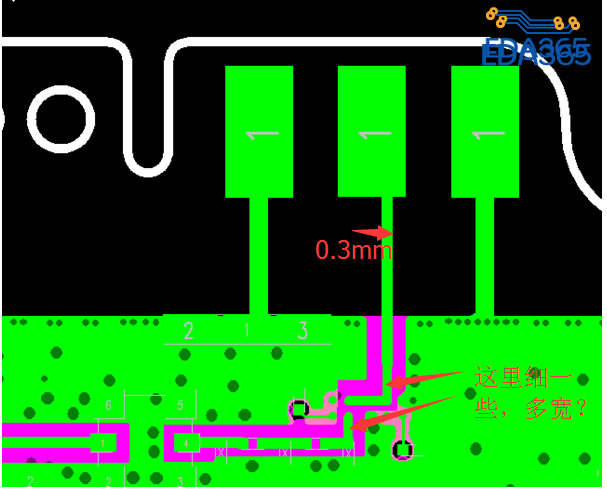

給製版廠說,參考L2層做50ohm±10%单端阻抗,他們會調整gerber中紅色阻抗線的線寬。這裡你可以先走6mil

如果板子的叠层不是你自己设置的,那么阻抗就交给板厂去做,只要你说明那些线参考那层做阻抗,板厂的工程师会帮你调到相应的宽度

要吗 你自已完全算好 要吗 你把要求给板厂 让他们控制

高亮后告诉板厂你要做阻抗,首先自己大概算下阻抗需要的线宽,把余量留出来即可

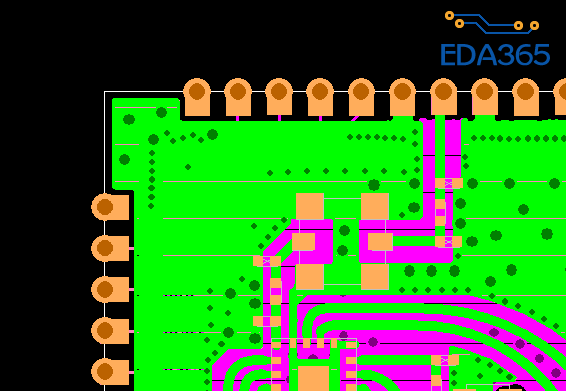

50欧姆如下图,0.3mm板厂数据,可能各个板厂有所不同,板厂为准。另问一句,小编图片上的元件是射频插头测试座吧?

50ohm, 5mil ,参考第二层,这就是板厂算给我的,现在把这段天线出来的线净空了(没参考层),走线要多宽?

对的,是这个座子。 你说的0.3mm是指净空处的线宽吗?有地平面参考的那些线是多宽?

走渐变线吗?有地参考的走5mil, 到净空没地参考的地方走6mil

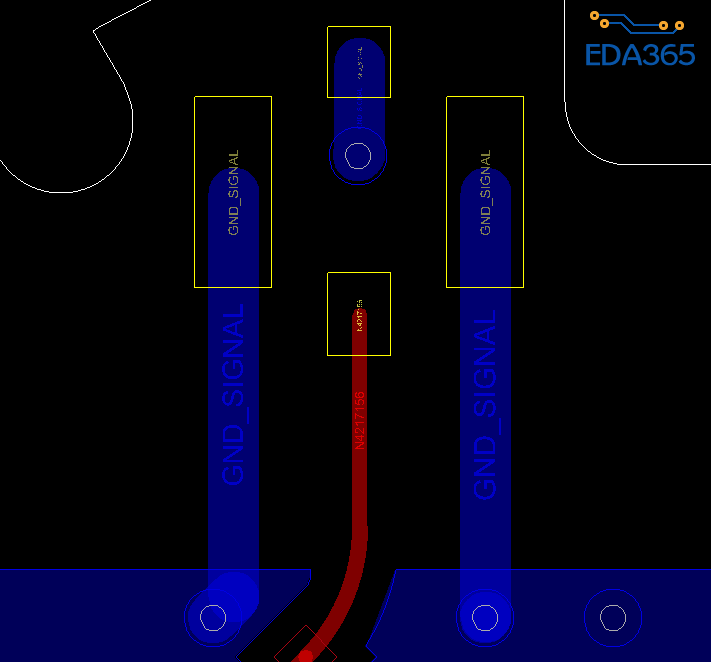

座子下面禁空是否对射频信号有影响那?

我司暂时没见过射频座直接放板端禁空的情况。可能信号不好与没有参考层有关

天线一般走default,也就是50ohm。线要平滑不能有折角,折角处走圆弧。线的周边要补gnd的shape并且下via每层一直,负片层对应走线的地方也要净空,补gnd的shape同正片一致