PCB edit 中修改及添加Net的方法

时间:10-02

整理:3721RD

点击:

环境:

1、cadence 16.6 x86;

方法步骤:

1)1.设置。setup/User preferences editor

将默认的保护开关打开,如下图所示:

可以通过搜索功能找到“logid_edit_enabled”

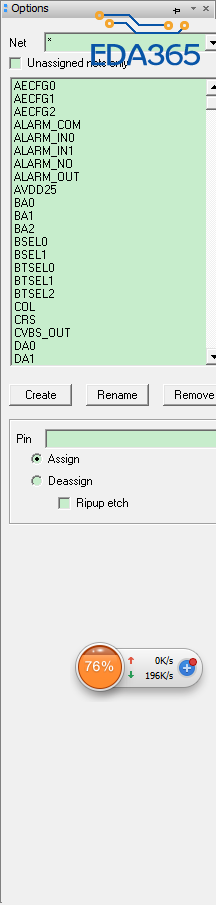

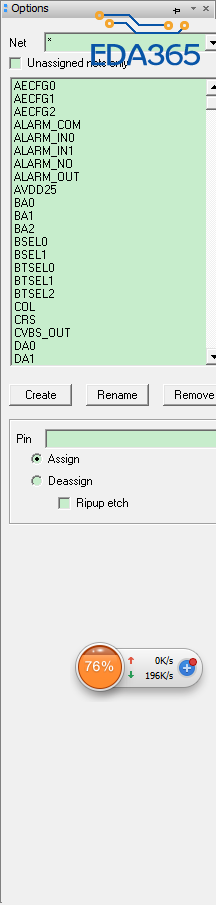

2) 运行修改网络Logic/Net Logic命令,可操作项目如下图所示

在此窗口当中,可以发现可以对net进行产生,重命名,删除;

我现在的问题是不知道如何将这个NC引脚接地。

1、cadence 16.6 x86;

方法步骤:

1)1.设置。setup/User preferences editor

将默认的保护开关打开,如下图所示:

可以通过搜索功能找到“logid_edit_enabled”

2) 运行修改网络Logic/Net Logic命令,可操作项目如下图所示

在此窗口当中,可以发现可以对net进行产生,重命名,删除;

这样更改完后,原理图会有什么变化吗

对原理图没有影响,但是改变了PCB文件的网表。

在原理图和PCB分别由不同的人设计的时候,这种做法不提倡的。

我主要用在下面的情况:

1、NC 引脚,但是在原理图中没有,但是在PCB中有。画PCB时又想把这些引脚又想接地,不知道在原理图中不修改PART的情况下,怎么修改?所以就想了这么一招;

当然建议最好不要这么做。

引脚不对应的话,网表怎么导入的?

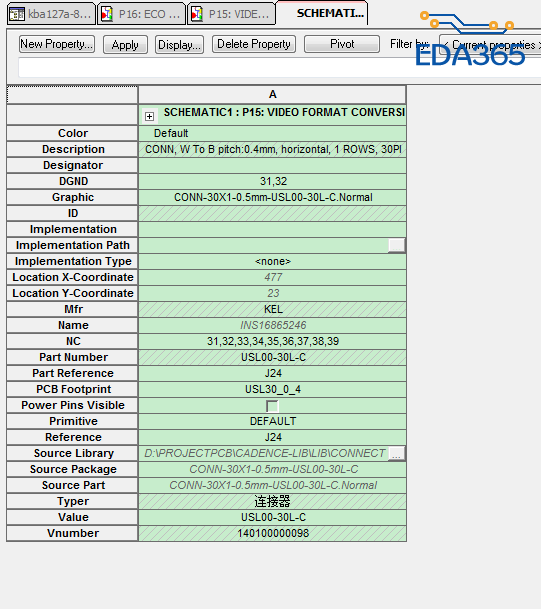

方法是原理图中选中PART,打开属性页。

增加NC名称,将对应的空引脚写入即可。

我现在的问题是不知道如何将这个NC引脚接地。

看来是原理图规范不一样,我见过的原理图的part没有NC属性,NC pin都是给了个Place no connect

NC 属性是可以自己添加的。你可以在帮助中了解一下

我知道可以自己添加,但是我见到的原理图都没有添加这个属性。

添加了NC的pin和直接连到place no connect(在原理图上就是连上了一个×)有什么区别吗?

學習了

学习了

不是一会事。使用NC引脚是因为原理图和PCB封装不对应:PCB中有多余的引脚后原理图中没有;

学习了

学习了。