电气规则里面设置的等长为何跟pcb里面网络显示值不同?

时间:10-02

整理:3721RD

点击:

电气规则里面设置的等长为何跟pcb里面网络显示值不同?

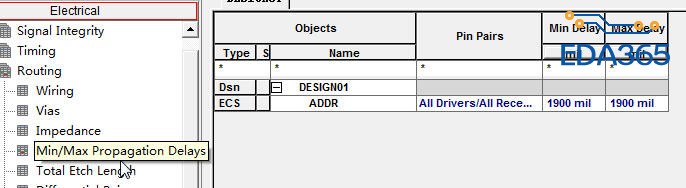

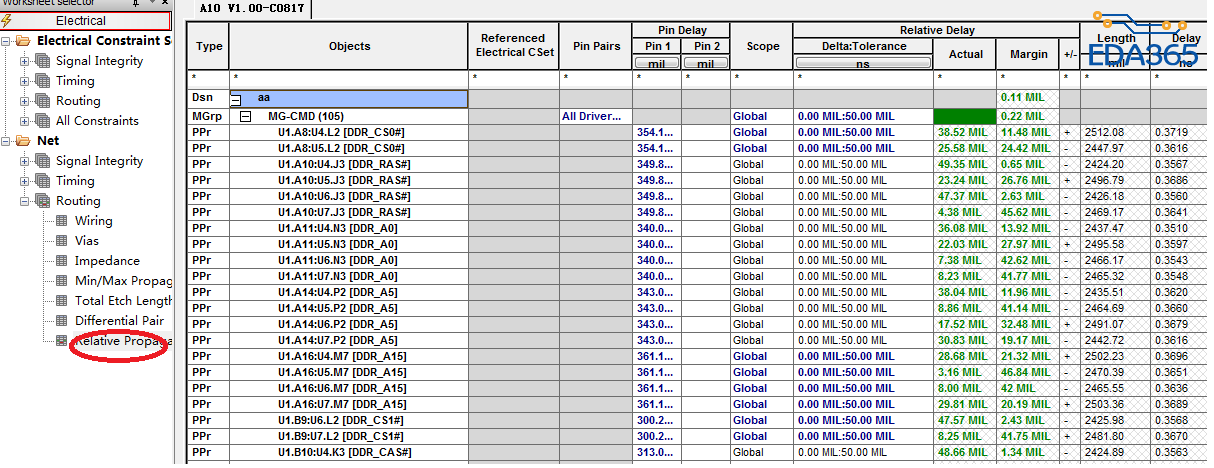

首先我在电子规则的Propagation delay设置一个固定值,最大最小都是1900mil,单位我切换成mil

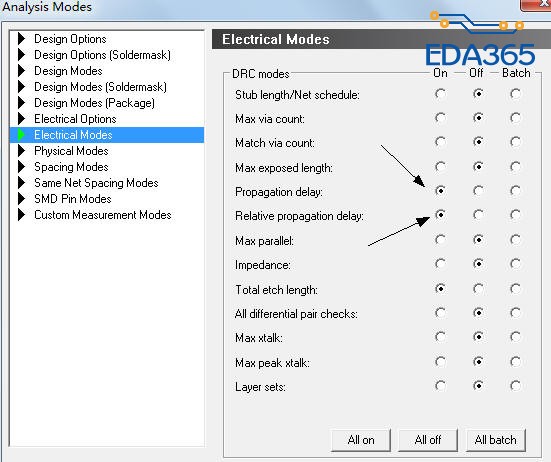

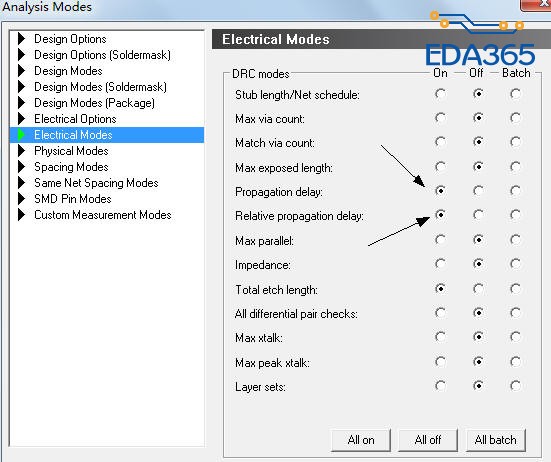

然后我在net里面的Propagation delay找到我要设置的网络,创建为匹配组;然后勾选上刚才设置的规则,然后点击analyze,打开相关的分析开关

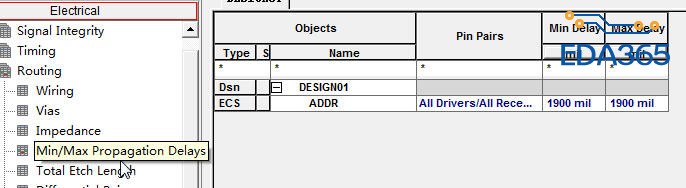

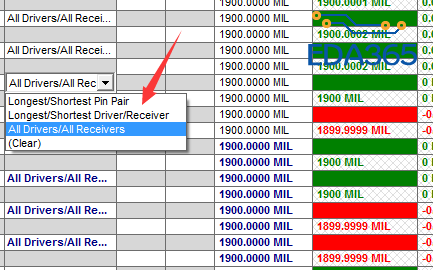

在pcb我先随便把这些网络线拉完,然后我选择所有网络右键执行一个自动等长延迟的选项,等待数秒之后,在规则里面可以看到这样的情况

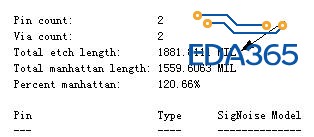

但我在pcb里面选择网络显示信息的时候发现这样的情况

难道没等长到设置的1900mil附近?

这里的设置会对布线有哪些影响?

像auto-interactive delay tune这个功能还能在哪里设置它的布局布线策略?感觉默认情况下 走出来的有时候不是很好

是否有规则可以限制于规范它?

首先我在电子规则的Propagation delay设置一个固定值,最大最小都是1900mil,单位我切换成mil

然后我在net里面的Propagation delay找到我要设置的网络,创建为匹配组;然后勾选上刚才设置的规则,然后点击analyze,打开相关的分析开关

在pcb我先随便把这些网络线拉完,然后我选择所有网络右键执行一个自动等长延迟的选项,等待数秒之后,在规则里面可以看到这样的情况

貌似等长是在这里设置

但我在pcb里面选择网络显示信息的时候发现这样的情况

难道没等长到设置的1900mil附近?

如何我要设置绝对等长 应该注意哪些事项?

这个误差是不是还考虑了过孔的z方向的长度?像打孔的话有2个,就要算上2个过孔的深度?

这里的设置会对布线有哪些影响?

像auto-interactive delay tune这个功能还能在哪里设置它的布局布线策略?感觉默认情况下 走出来的有时候不是很好

是否有规则可以限制于规范它?

我定义了一根差分对的长度是3500mil,自动走完之后 在规则管理器里面显示的是分别3488mil与3499mil

但是在pcb里面现在net查看的时候发现是4566mi与4595mil

这个又是怎么回事?

等长以规则里面的为准? 那多出来的部分咋么解释,如果短了 还能理解可能是叠层的原因 这个是啥原因?

最大最小延时不要设置成相等。

如果要设置成绝对等长的话一般如何做?不是最大最小都设置成一样吗?

或者在应用中一般如何处理会比较好,实际布线优化的时候发现基本在allegro里面很难做到全等长!不知道是否跟设置有一定关系

我之前使用pads,基本在自动优化等长的时候 都能做到0mil误差

既然有最大最小,为什么要设置成一样?如果设置成一样,干脆就只给一个目标参数就好了。

我的理解,等长一般是相对等长,以某个信号为基准(如:clk),然后允许范围内+-偏差,像小编这样做等长就是绝对等长,完全一样,很难

还有你MIL单位已经很小了,精度就没必要到小数点后4位,只要两位数,就够了吧