10g信号背钻要求,求大伙确认!

时间:10-02

整理:3721RD

点击:

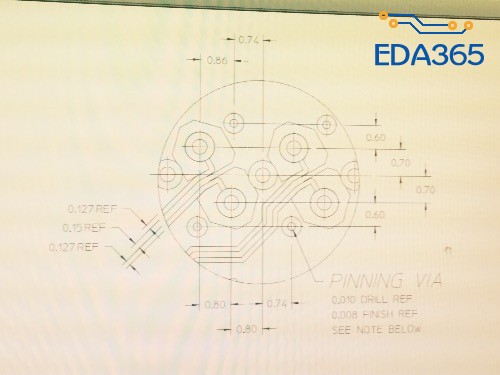

针脚通孔15mil,焊盘外环15mil,背钻的区域有多大?

附上datasheet的设计要求。

附上datasheet的设计要求。

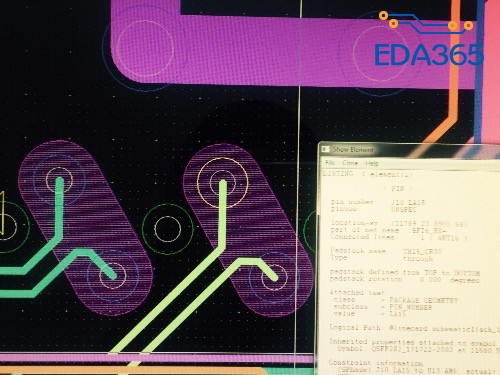

我画了个antich铜皮表示掏空的区域,请大家确认这样做对不对,还是按照设计要求呢

这个不是挖空plane层么,,你所谓背钻不会指这个吧...

你这背钻。

提取背钻符号,用文件描述给板厂。

你的datasheet说的是挖空的示意,具体是用你自己画的还是datasheet上的要看你们SI的要求了,背钻和anti pad是不一样的,anti pad只是避开铜箔,背钻是要把基材也钻掉的,这个要和工厂确认15mil成品孔的尺寸他们用的钻头是多大,然后在左右两边增加至少7mil的安全间距,背钻深度要和连接器厂家确认最小要留多少深度,通过计算告诉厂家哪个是must cut layer 哪个是must not cut layer

是的,区域大小有什么经验可以参考吗?

谢谢,我就是按照你这个去弄得。

你这铜皮怎么弄的,是SKILL嘛,能给我下吗,万分感谢