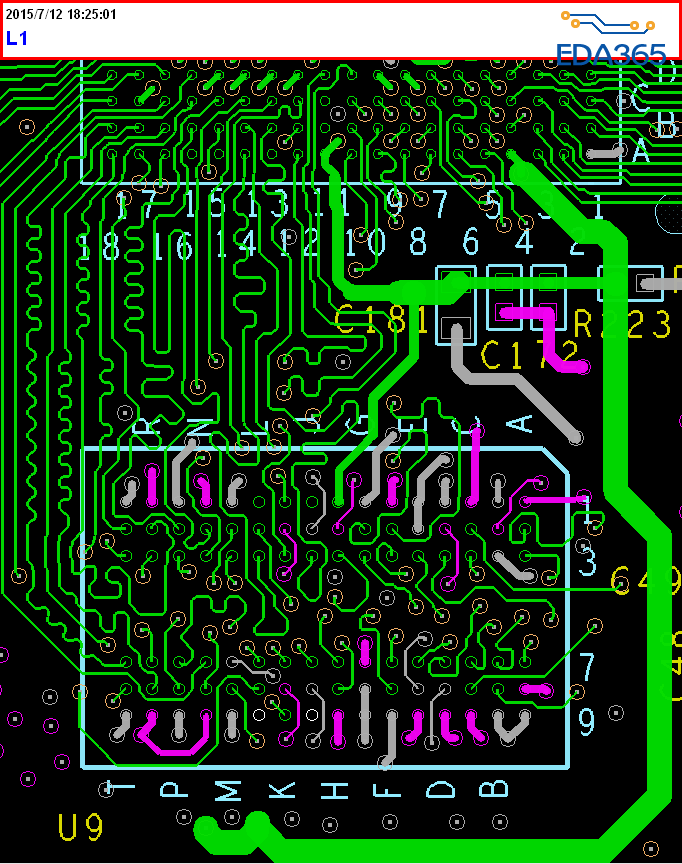

DDR3 data线走内层还是表层

时间:10-02

整理:3721RD

点击:

照常理的叠层为:

TOP-GND-POWER-BOTTOM(其中表层走信号线,内层不走线已保持参考平面的完整性)

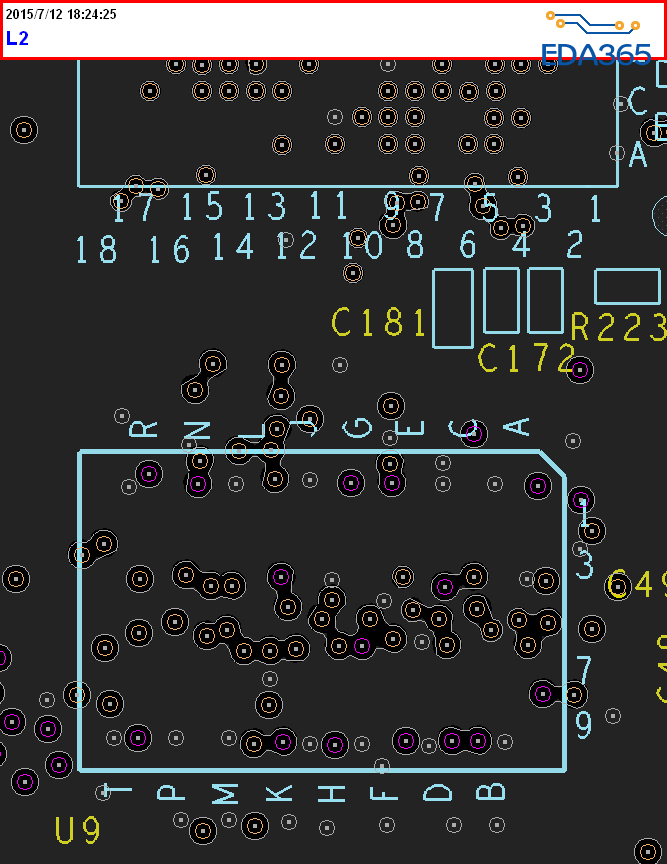

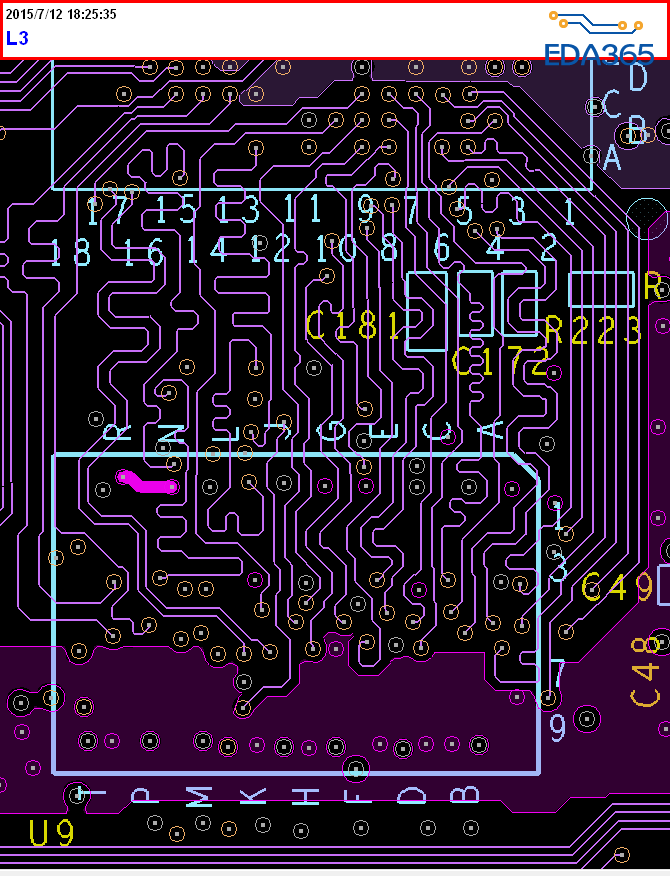

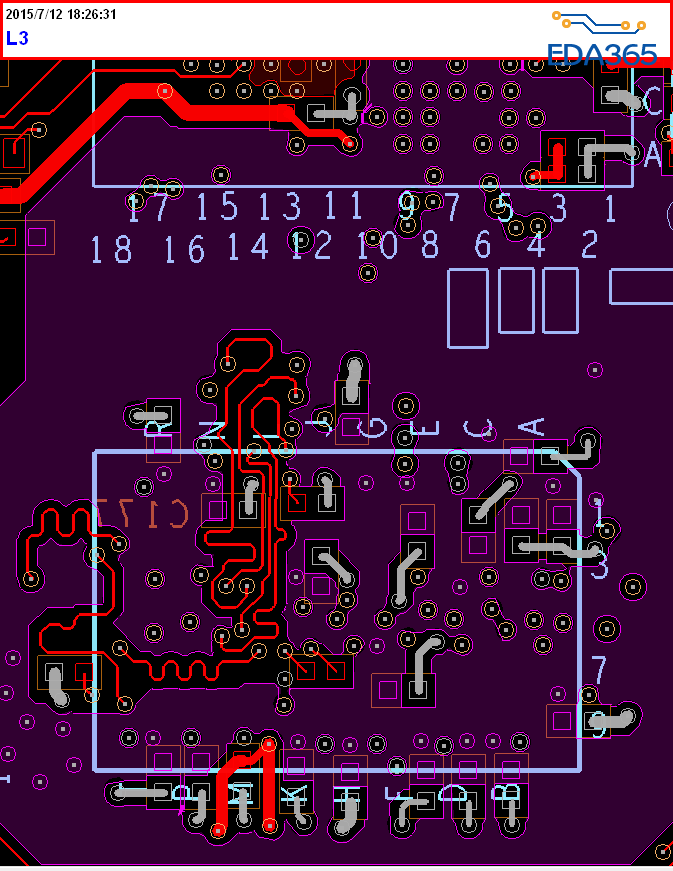

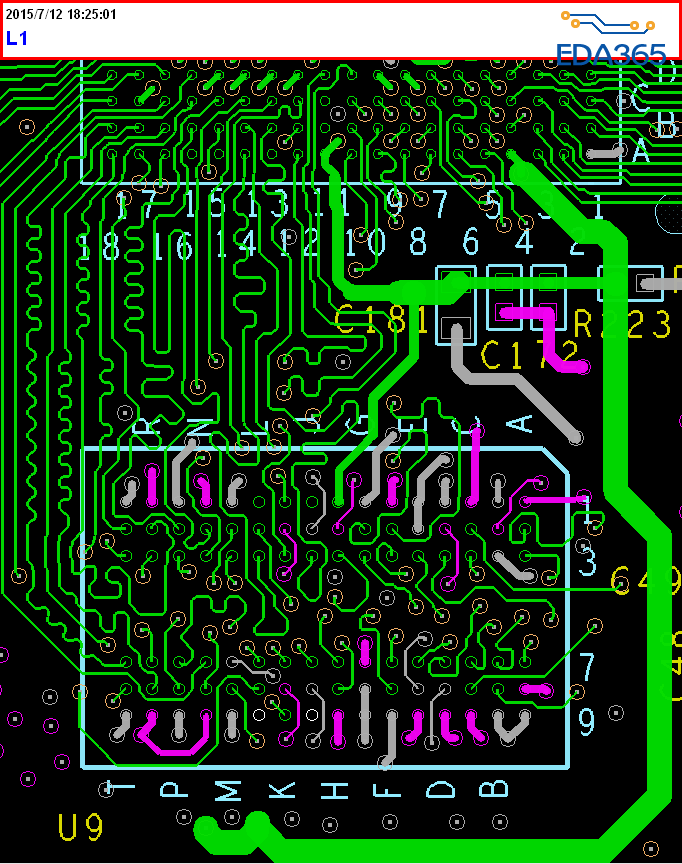

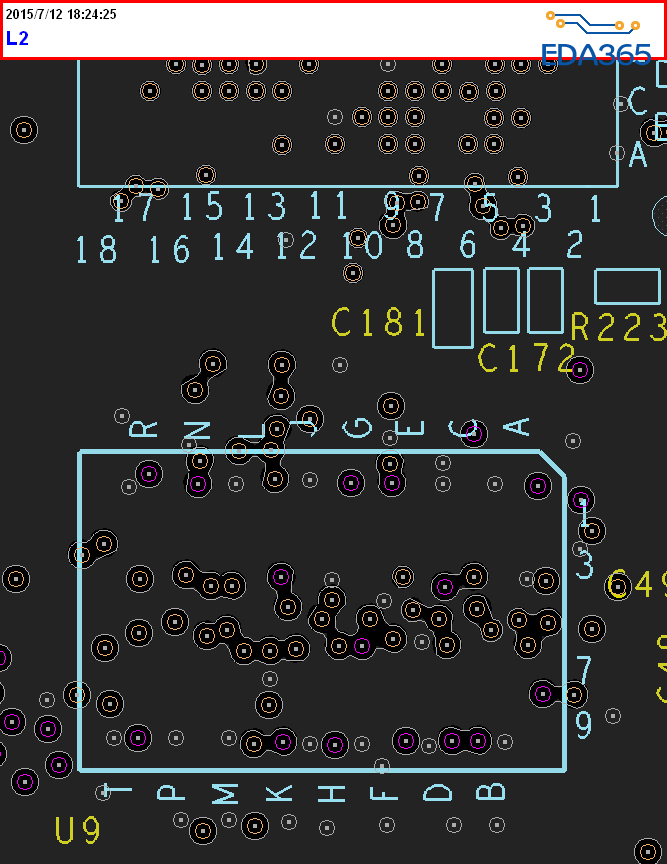

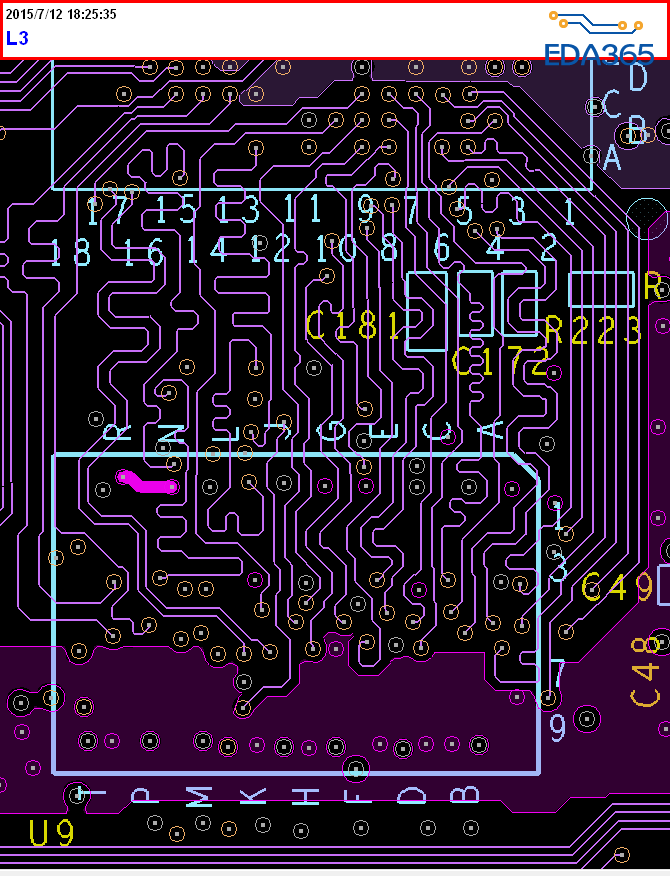

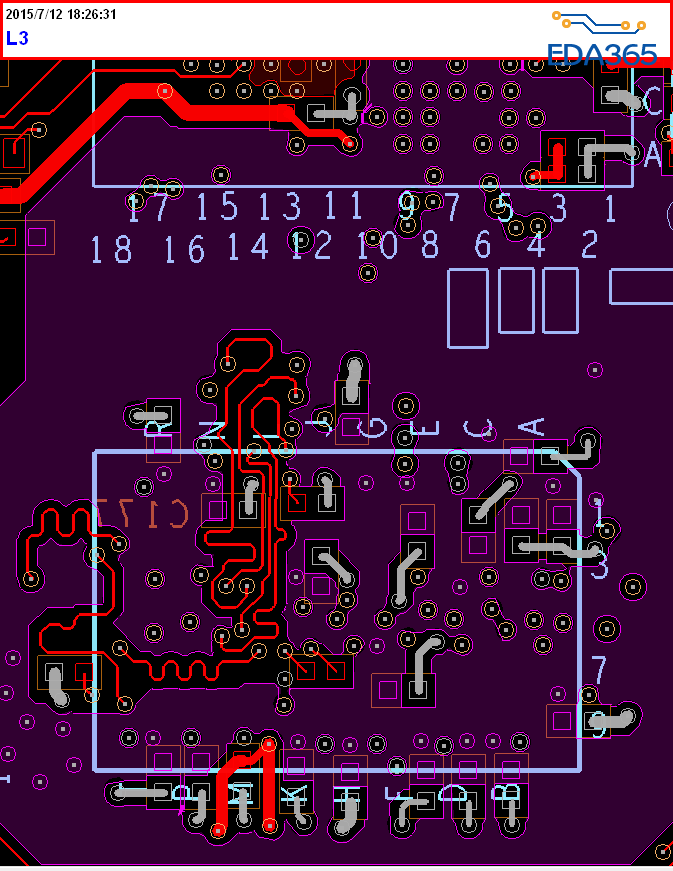

但是最近看见一份ddr3的layout guidelines,里面说data信号要走内层,addr和control可以走表层,局部叠层为

top(addr,control)-gnd-signal(data)-bottom(power)

如下图

求助,我要按常规走吗?如果按照开发板,信号走在里面tune的空间大点,还能有效减少EMI。但是刚在群里问有人说加工不方便,不是很理解。

求助,我要按常规走吗?如果按照开发板,信号走在里面tune的空间大点,还能有效减少EMI。但是刚在群里问有人说加工不方便,不是很理解。

[img]file:///C:\Users\kepo\AppData\Roaming\Tencent\Users\398515912\QQ\WinTemp\RichOle\SKXSEBCMC8IDFEH4OAY[P]E.png[/img]

TOP-GND-POWER-BOTTOM(其中表层走信号线,内层不走线已保持参考平面的完整性)

但是最近看见一份ddr3的layout guidelines,里面说data信号要走内层,addr和control可以走表层,局部叠层为

top(addr,control)-gnd-signal(data)-bottom(power)

如下图

求助,我要按常规走吗?如果按照开发板,信号走在里面tune的空间大点,还能有效减少EMI。但是刚在群里问有人说加工不方便,不是很理解。

求助,我要按常规走吗?如果按照开发板,信号走在里面tune的空间大点,还能有效减少EMI。但是刚在群里问有人说加工不方便,不是很理解。[img]file:///C:\Users\kepo\AppData\Roaming\Tencent\Users\398515912\QQ\WinTemp\RichOle\SKXSEBCMC8IDFEH4OAY[P]E.png[/img]

说说我的看法,其实任何信号都可以走表层或者是内层,就看你是你什么样的要求,对于你这个产品,个人认为应该是走在表层,因为是4层板,为了保持参考平面我完整性、信号完整性和电源完整性,走表层是比较合适的。

双面板。

个人也赞同一楼所说的!

看你到底有多少个层喽,如果一个4层板你还想怎么走

4层板,如果可以那样走,data走内层好处是很多的,不信你可以试试看。

如果是多层板可以考虑走内层

是4层板

我也觉得好处是走线空间和EMI问题,而且参考平面也是完整的没有被破坏

你觉得好在哪?

走在表层感觉好处没有走在里层多 但是我看实际的产品中还是走在表层的

学习了

等高手;来解答

个人觉得 走内层的话,那就把所有信号线都走内层(主要DDR),然后表层(顶层或者底层)铺铜,另外一层表层走少量信号线,参考完整地平面在信号层和表层电源层之间,这样电源和DDR都是以完整地为参考和回流,

学习了。