关于挖空铜皮成椭圆形的简单处理方法

时间:10-02

整理:3721RD

点击:

能不能够通过设置来达到在想要挖空的地方挖空成自己想要的大小,如果手动来挖空感觉太麻烦了

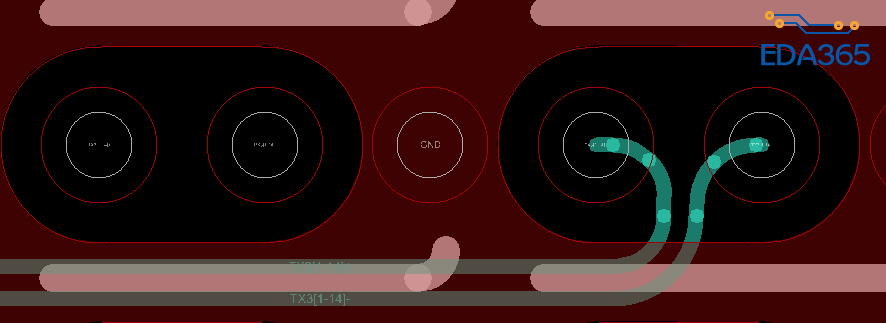

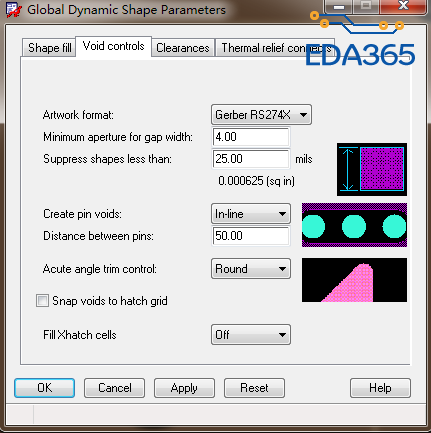

看图不说话,把pin void修改下,然后根据你的约束和实际情况输入合适的间距,一就可以了。但是比较坑爹的是暂时没找到局部设置,是全局的,不能写太大不然 BGA下方就铺不上铜了。 最快捷的还是用skill 论坛貌似有记得

如果只是内层自动生成的铜皮要避让的话,自己画一个Anti Etch的铜皮即可。这样生成内层的时候就会自动避开的。如果表层也要避开,就加一个rout keepout。

同层是可以,但是没看到如何针对几个引脚或者过孔设置,比如只针对差分过孔,其他所有过孔引脚都不设置,这样最科学,当初找了好久没找到。LZ找到更好的了说下,我现在一般都是画个keepout 复制下,还是比较烦

找Rock开发skill吧

画是很简单的,两个圆加一个框,合并一下就OK了,这种避让一般都是高速差分线需要做的特殊处理。画一个好了,然后按照VIA的位置依次复制过去就好了。现在高速板子上自己都是这样处理的。如果有更好的方法希望分享一下~