高速蛇形线

时间:10-02

整理:3721RD

点击:

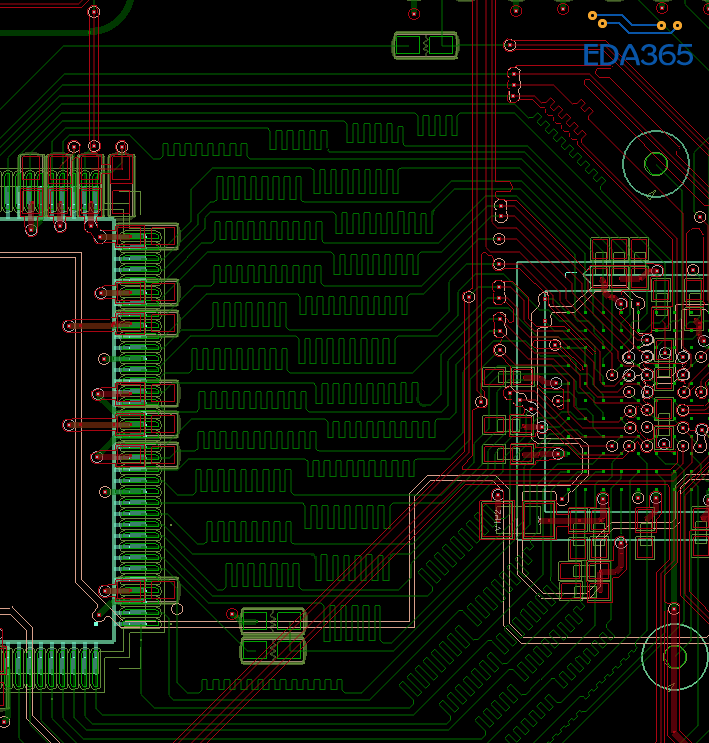

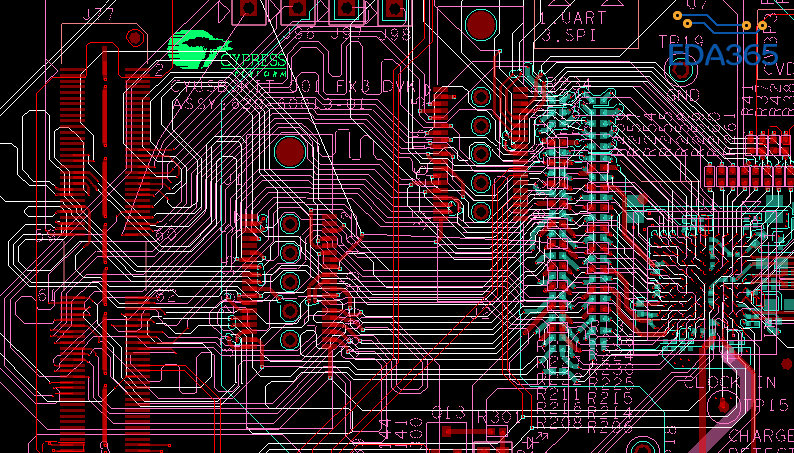

最近做了一块板USB3.0芯片和FPGA之间32数据线可以跑到100M,我走线走的是蛇形线(等长误差50mil),如图所示,把我的设计发给CYPRESS的工程师审图,他们说没有没有走过高速蛇形线,他们都是走直线的,他们给的参考版,如下图所示。我这杨会不会有问题?100M有必要等长吗?100M的等长误差最大是多少?

我的走线

官网产考

自己定一个

帮你顶一个

顶一个

有问题,速率100M的等长误差可以很大的,你这50MIL相对来说很小了

查芯片datashite,上面都有写

给出的是50mil 我走的也是50mil 怎么不走蛇形线还得等长?

等长不一定非要走蛇形线

走蛇形线,也没有问题,10G以上的速率一样可以走。

问问硬件嘛

顶一个

看参考板也有做绕线的动作,估计误差比较大一点,而且还接到子板去了,子板情况未知。

100M的还好吧?不用做到50这么小吧?

100M的等长误差一般是多少啊?