PCB板出来后只能降频使用。

小弟顺便想问一下,如果把6层加成8层的,增加1层地,一层电源,是不是会好呢?还是说增加两层地效果会更好?

自己跟开发板对比一下,看看什么地方没做好,“DDR有一部分线做不了50欧姆阻抗匹配”,要看失配的严重性,方便的话把文件放上来看看。

内存线要有完整的参考的平面,不管是GND还是电源

今天好好问了一下软件,都说是内存的问题,在内存跟CPU之间的交互频率在95MHz以下跑起来基本都没有问题,只要超过100就不行。这颗芯片是133MHz的设计频率,我就有点想不通了,95都能跑起来,为什么100就上不去了呢?没道理啊。如果是内存走线匹配问题,那么应该说是根本就能不能运行才对啊。我只能发发截图,文件什么的是公司的,还是要保密的。

我内存频率在95Mhz以下跑起来都没什么问题,就是超过100之后就会卡死。这个的影响就会有这么大么?我的想法是加到8层,增加两个平面,一个作为GND,一个做PWR。实在不行就两个地层把中间全都包起来。不知道哪一种效果好。

可能时序裕量刚好在95MHZ左右用光了,再提高频率时序就不够了。

这个怎么理解?时序裕量这个是受等长影响还是说受阻抗影响呢?

因等长、反射、电源噪声等问题造成时序裕量偏小。

好吧,谢谢了。我再研究研究,不行就考虑加层做阻抗匹配。目前有一个好消息就是把1.8V电压降下来之后,频率反而能上去一些了,100MHz已经攻克了。我打算继续实施降降电压试试。就是有点想不通为什么。

拿仪器测试一下哈

能发截图也成啊,不发上来大家不好给准确的建议。

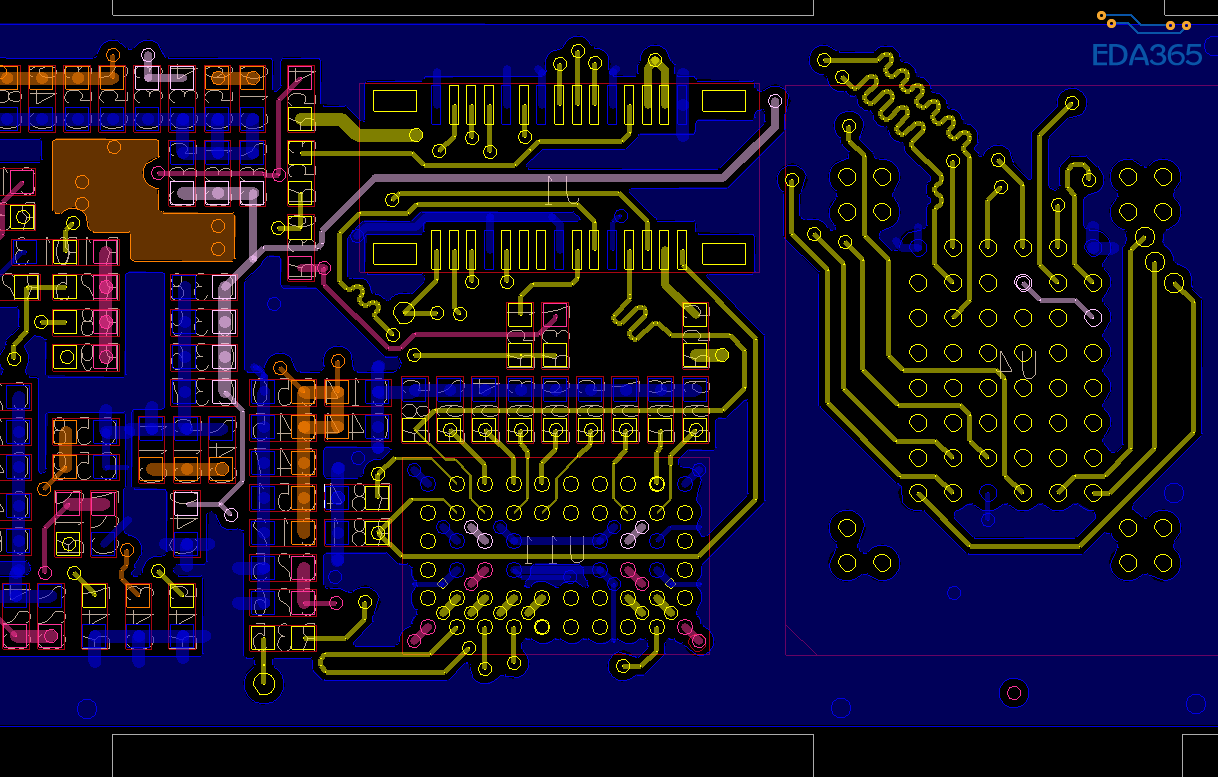

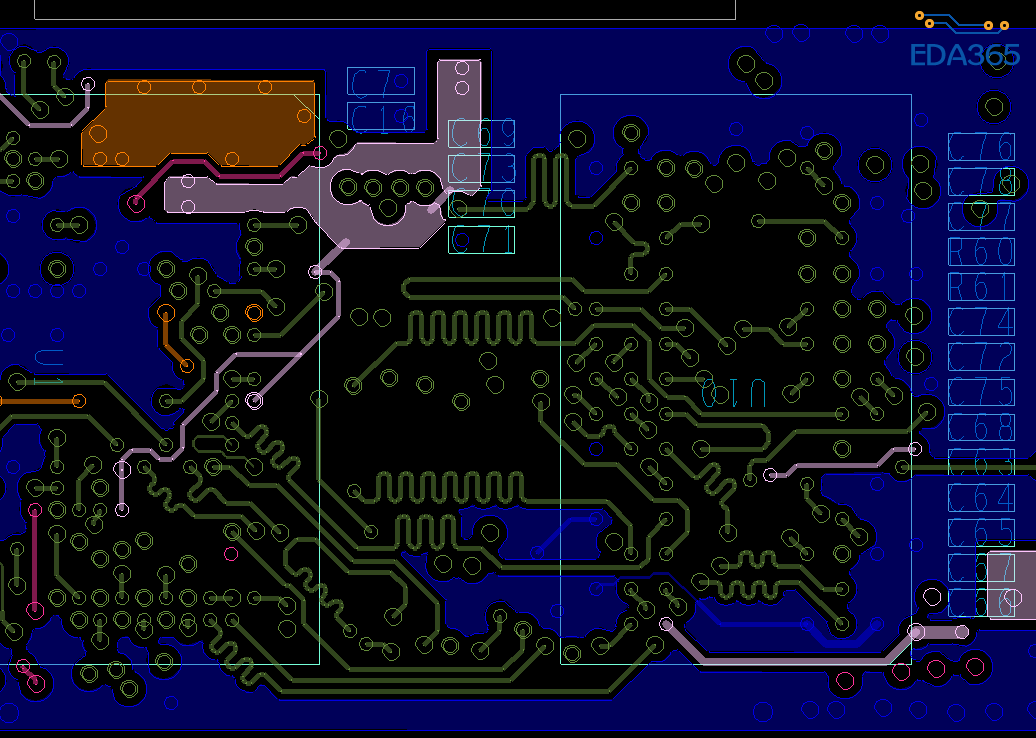

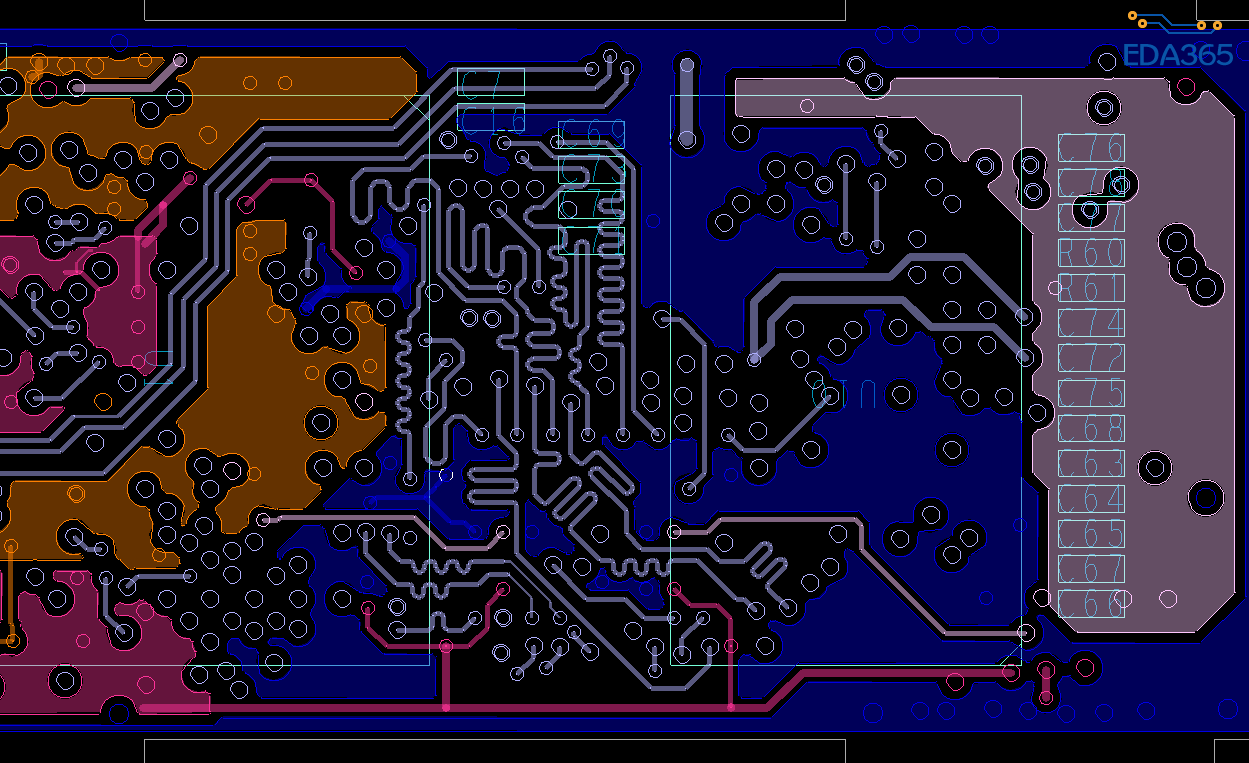

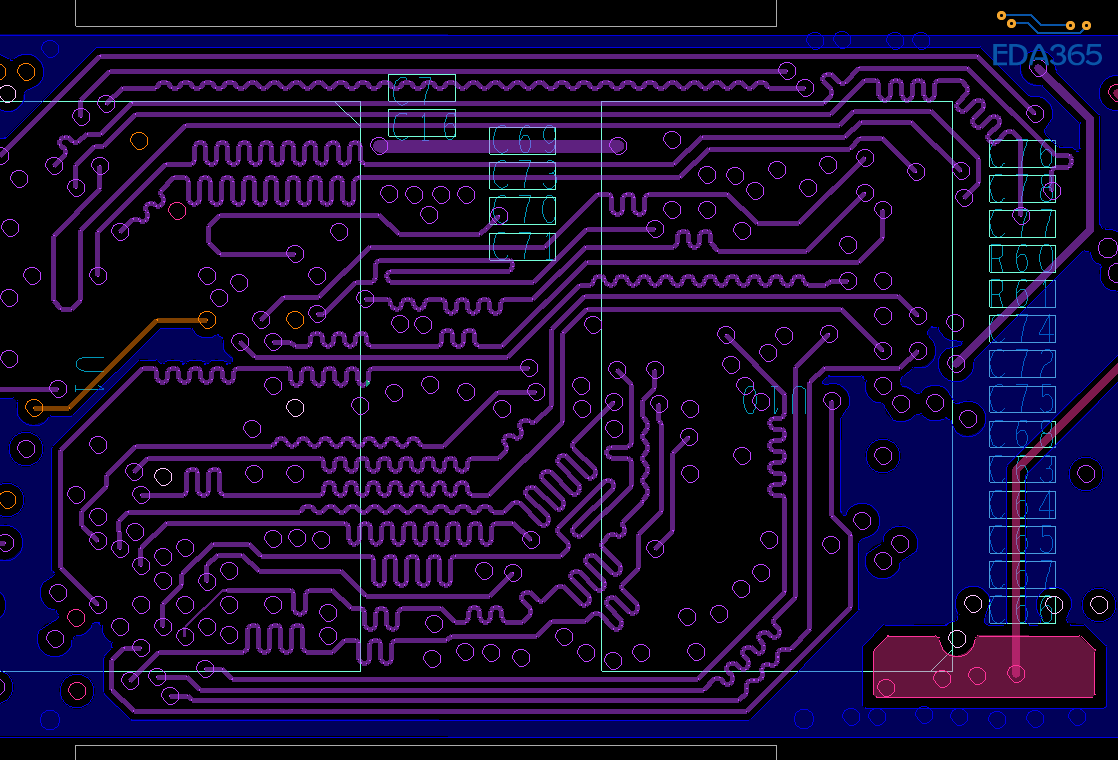

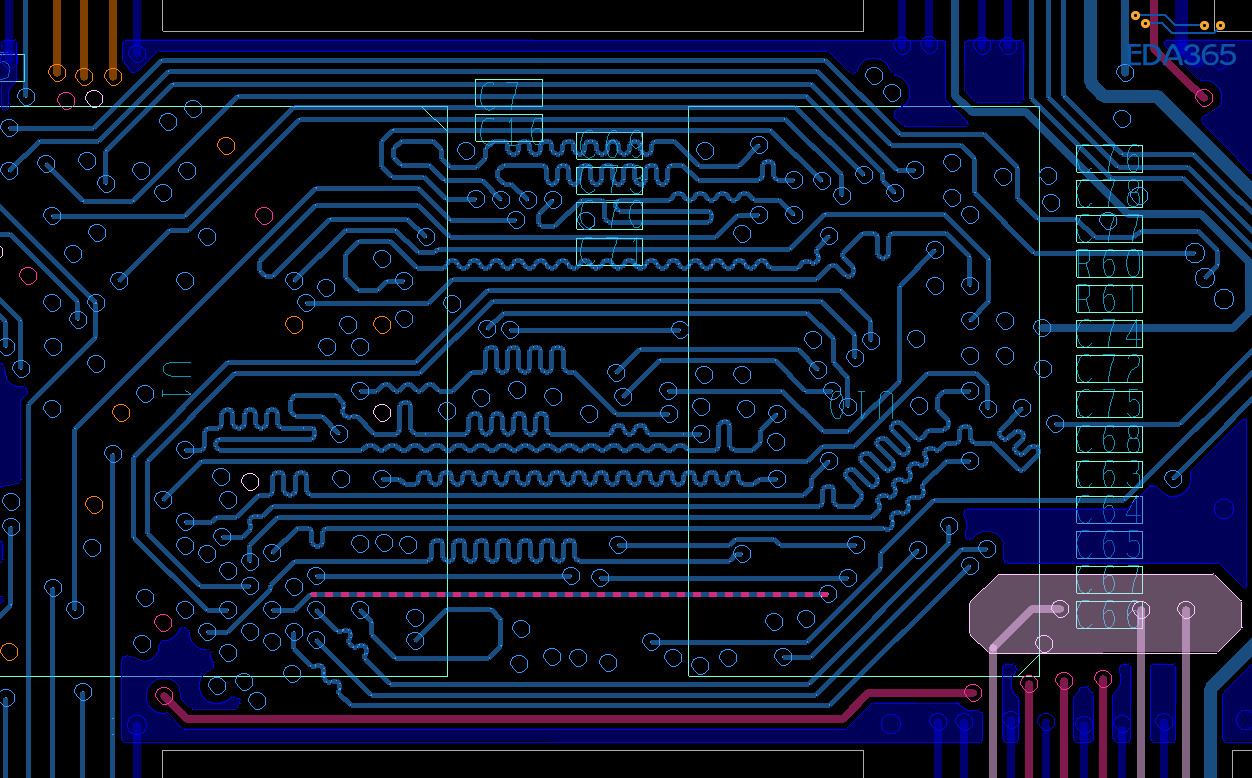

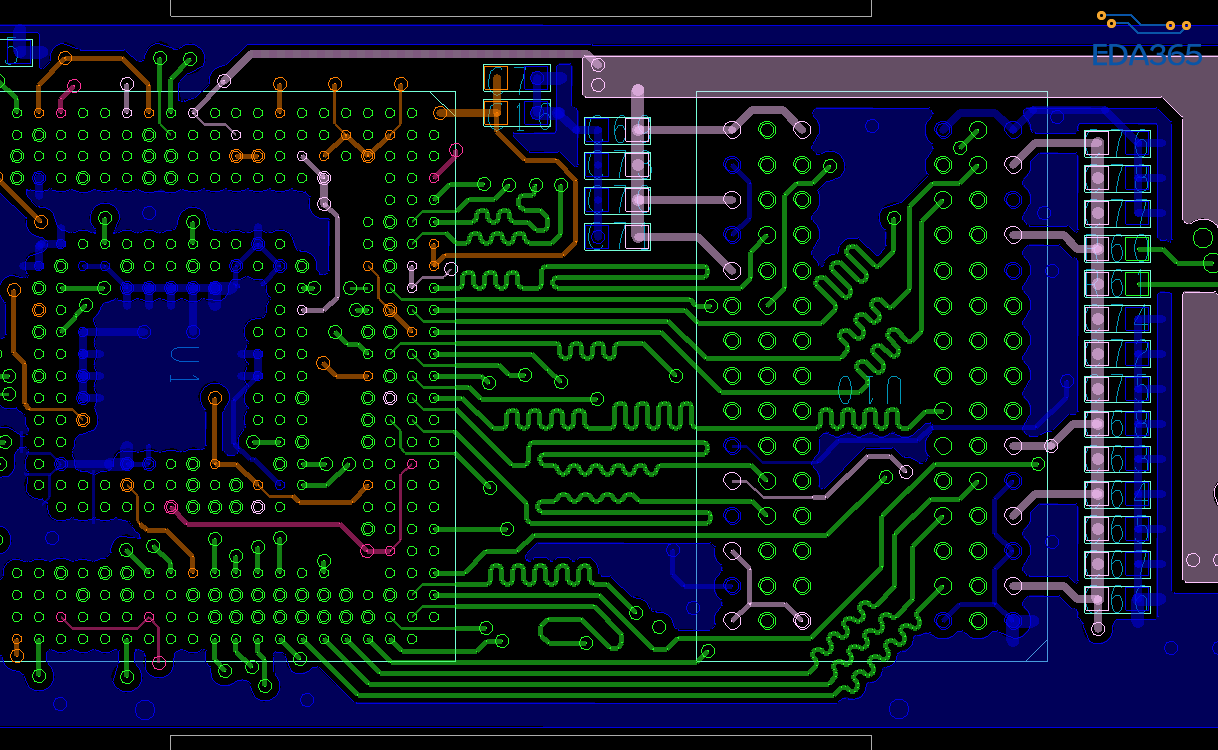

小弟的图如下,顺序是TOP-GND-S1-S2-PWR-BOT。目前的情况是把1.8V的电压降下来了,降到了1.47V之后,现在CPU主频在532MHz,内存频率在133MHz的时候可以运行了。但是CPU是可以在667MHz的频率下跑的,现在跑不起来。还在查找原因。望大家都看看,有没有遇到同样的问题,给小弟一点建议。

bot

gnd

pwr

s1

s2

TOP

你这几乎就没有参考层啊,层间串扰会很严重,加层吧。

还好只是一片DDR,不然降频都没用。

内存线要有完整的参考的平面,不管是GND还是电源

能跑起来是个奇迹