DRC ERROR 这个怎么破

时间:10-02

整理:3721RD

点击:

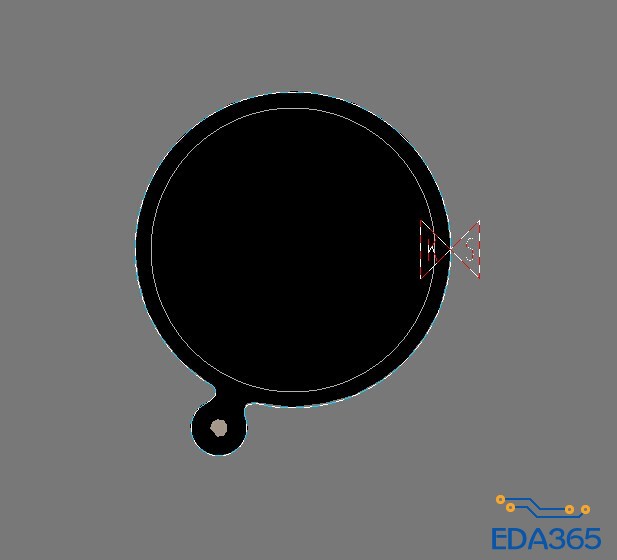

LISTING: 1 element(s) < DRC ERROR > Class: DRC ERROR CLASS Subclass: POWER Origin xy: (19099.125 7276.170) Constraint: Shape to Route Keepout Spacing Constraint Set: DEFAULT Constraint Type: NET SPACING CONSTRAINTS Constraint value: 0 MIL Actual value: 0 MIL - - - - - - - - - - - - - - - - - - - - Element type: SHAPE Class: ETCH Subclass: POWER Part of net name: 3.3VD - - - - - - - - - - - - - - - - - - - - Element type: SHAPE Class: ROUTE KEEPOUT Subclass: ALL

中间那个圈是outline 板框

shape重新避让也不行?

shape是正片的动态铜,重新update也还是一样,貌似与route keepout之间,它不自己自动避让规则设定的间距

移动一下铜试试还有没

没有用的,各位做下实验,看看有没有这个问题

我的动态铜皮没有这种问题,动态铜皮能正确避让开keepout。你删掉shape重新试一下吧。

或者用静态铜不行么?

我是最后,手动把那块铜皮挖大点,问题解决了,drc不报错了。但我板子不止这个keepout孔,其它的一样的孔没有报错,估计是软件的bug,多谢各位高手的关注。

;P;P

修改线距规则应该也可以