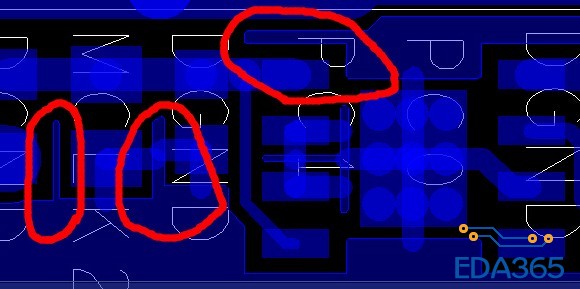

通常大面积敷铜后会出现不合时宜的边边角角,有设计规则设置可以使之不出现么(如图)

时间:10-02

整理:3721RD

点击:

如图,使用大面积敷铜时,在pad与pad之间,或者pad与走线之间空间较小时,此时敷铜不完整,可以通过规则设置来限制么?

铜箔参数设置中Void controls里面的Minimum aperture for gap width的数值表示最小铜箔宽度,设大点;还有Suppress shapes less than表示最小铜箔面积,也可以设大点。

通过这两个参数可以减少很多细小的铜箔产生。

可适当增大shape to pad的间距设置,个别的地方可以挖掉

尝试过加大距离了,但是有些地方还是没法避免,特别是板子规模比较大的时候,这么处理起来就比较麻烦

谢谢dzkcool的耐心解答,找到了与altium designer相对应的设置。

mark一下

这个问题确实很烦,有必要上静态铜箔

mark下

小编的方法很实用,赞一个

学习一下,谢谢!

学习了

请问下小编是如何解决的

你指的是cadence还是altium designer?

cadence,谢谢

按照如下操作:shape->global dynamic params...“轰隆隆。隆隆。”蹦出一个对话框,选择Void controls,再设置参数。小编dzkcool已经说过了