布局时元器件对齐问题

时间:10-02

整理:3721RD

点击:

在布局时为了快速摆放,有将格点设置成大小网格如5 5 5 5 5这种做法。我在布局时将格点设成25 25 25 25 25前提下,去摆放元件,发现即便相同封装同一NET属性的元件也会有无法对齐的情况,请论坛上知道的朋友解释一下原因,有没有方法可以改变?

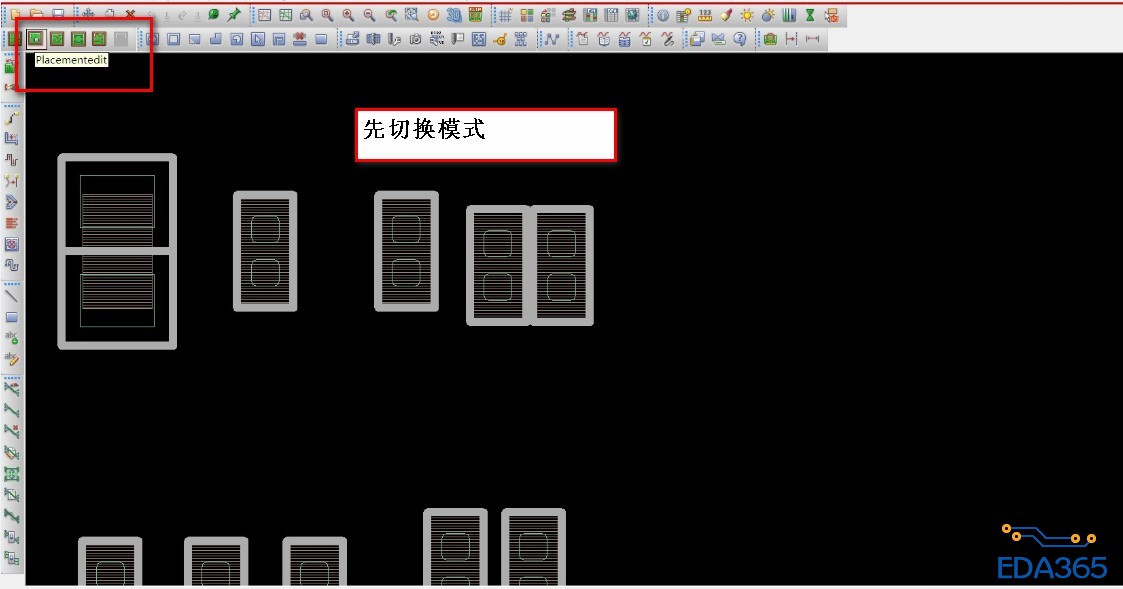

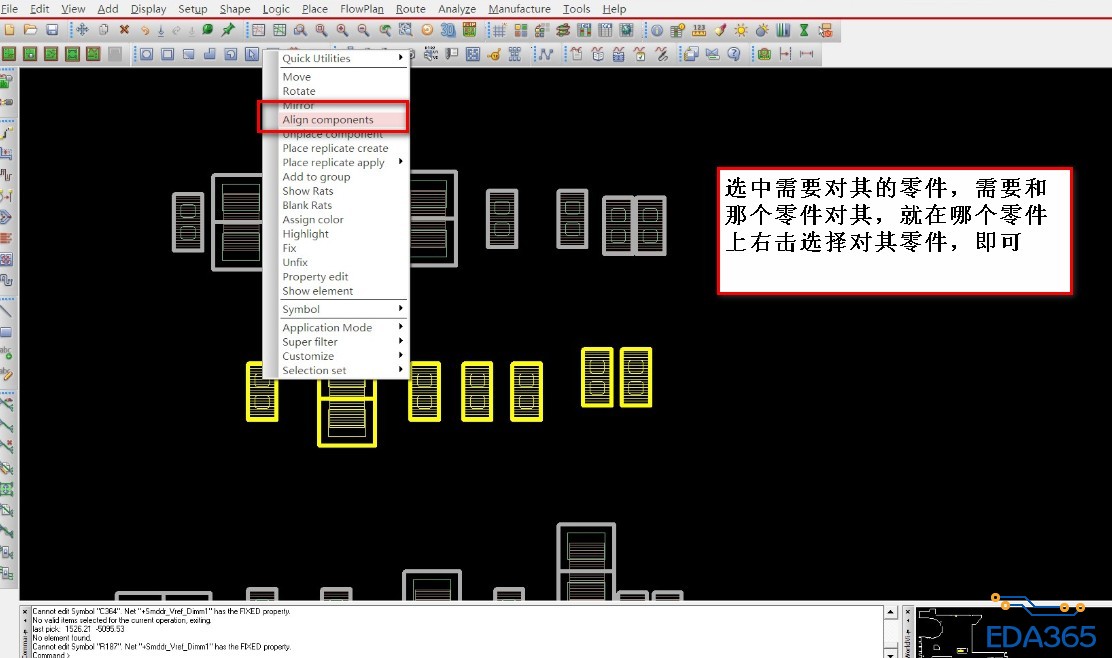

若是同一封装,还不能对齐,你可以试一下这个。

参考以上图片

可能是建库时的栅格间距与布局时的间距不匹配造成的,

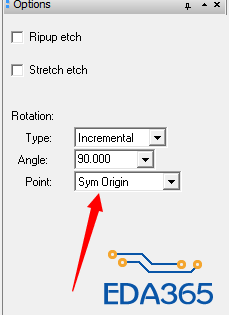

以后移动器件时试试在options里面的Rotation改一下设置

这种问题一般是移动器件的时候选择的模式有问题,当器件本来没对齐,而选择user pick抓取模式,那不管你设置多大格点还是对不齐

确实我们建库时栅格参数设置很乱没有统一,若是不同器件需要对齐,相信这是有影响的。但是现在同一package在同一brd板上出现移动时无法对齐,那么应该不是库的问题吧。之前了解到PADS工具就有这种库与brd板的关联。觉得楼下说的抓取器件时模式选择的原因可能性大 因为我确实用了USER pick。以后建库会对参数设置一致起来。谢谢各位回答。

16.5版的吧,我16.3版的没看到这个功能呢.

正解。通过换一下抓取命令就解决问题了。谢谢回答。

哈哈现学现卖

学习,跪谢

学习了