原理图Design Rules Check后发现的错误怎么解决

时间:10-02

整理:3721RD

点击:

有好几个错误类型,截取出来:

WARNING: [DRC0004] Possible pin type conflict P1,NCE Bidirectional Connected to Power

SCHEMATIC1, FPGA_CONFIG (320.04, 96.52)

WARNING: [DRC0007] Net has no driving source N5154057

WARNING: [DRC0006] Net has fewer than two connections N5154057

WARNING: [DRC0040] The off-page connector does not have any wire connected. PXI_LBL0

WARNING: [DRC0038] Visible unconnected Power Pins are connected to global nets X1,PXI_LBR5

百度了一下,网友说04,06,07,40这几种错误是可以忽略,可是一直找不到38这种错误的解决方法。

求大牛给点指导,不胜感激!

WARNING: [DRC0004] Possible pin type conflict P1,NCE Bidirectional Connected to Power

SCHEMATIC1, FPGA_CONFIG (320.04, 96.52)

WARNING: [DRC0007] Net has no driving source N5154057

WARNING: [DRC0006] Net has fewer than two connections N5154057

WARNING: [DRC0040] The off-page connector does not have any wire connected. PXI_LBL0

WARNING: [DRC0038] Visible unconnected Power Pins are connected to global nets X1,PXI_LBR5

百度了一下,网友说04,06,07,40这几种错误是可以忽略,可是一直找不到38这种错误的解决方法。

求大牛给点指导,不胜感激!

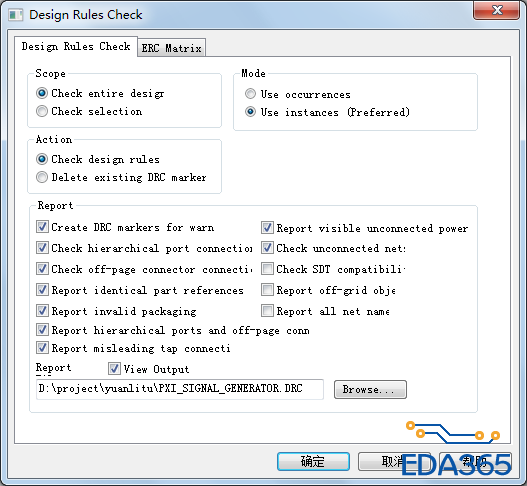

这个是设置

个人觉得WARNING问题不大,只要连接关系正确,然后package通过应该就没多大问题,只要没有Error就好……

设计规模上去之后,还是需要规则来好好约束的

這個問題犯了基本的低級錯誤. 有沒有關係 ... , 應該還好...不一定喔.

如果該訊號是輸出用 , 這很明顯線路設計是有問題的.

我猜應該是在 DRC metrics 裡面設定不正確導致有此問題.