对外接的网口如何做挖空处理

不是说信号高压,差分是不高,但是这一部分是要接网线的,从变压器往外走,网线会被雷劈,会被人碰到等,反正各种情况,所以网口部分一般要坐防雷(设备应用场合,室内/室外),起码要有ESD防护,当然有的芯片比较强,可以省略。

但不管怎么说,这一部分通过网线对外连接,外部情况是未可知的,所以必须考虑到位,从防护角度,作为高压处理。

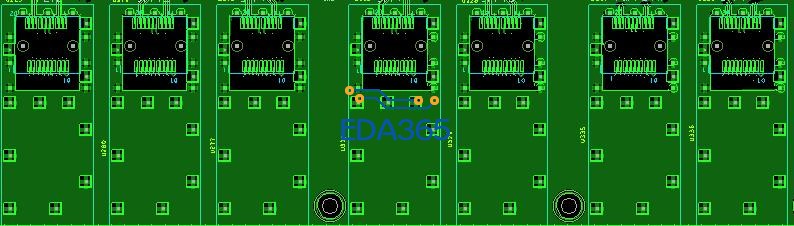

这些是光模块吧,不是随意挖空的,网口部分前面一点全部挖掉,一般是PGND单独铺铜过去

内层也需要避开吗

应该每一层都挖空处理

全挖空的话挖空部分铺上route keepout的shape,subclass选all

部分层挖空的话,正片层铺route keepout的shape,subclass选对应的层

负片层的话铺anti etch的shape,subclass选对应的层

空几层可以自己控制

是通信用的网口,可是你的怎么看怎么是光口啊,能不能上传图片看下网口的,我想着要是全部挖空的话,差分线的参考平面不是没了吗?很是疑惑,手上也没有参考的设计

你网口地下有地,但是网线就8根,里面没有任何一根是接地的,也就是说,即使你铺地,保证阻抗了,也没用,一到网线,阻抗连续性就没了,这时候,只有差分线之间的互相耦合,没有任何参考平面。

所以,从变压器到网口的部分,如果你没有防雷的什么走线或者铺铜,不用考虑阻抗了,那也自燃没有参考平面什么的了,而且这一部分属于高压,普通地也不应该铺到这里来的。

kevin大神正解..

明白了,谢啦

那我的网口要是自带的有网络变压器呢?这个也要挖空吗?

我也是这样想的,可是我见到一个客户的竟然挖空了

谁有这方面的资料或者参考设计,能不能发一个上来呢,我也正好遇到这个问题,不知道该怎么挖空

请问一下,网络芯片到变压器前级的线的阻抗是怎么保证的呢?变压器也没有接地引脚呀,有的变压器中心抽头是接电源或悬空的,那这段线的阻抗参考什么平面来做呢。岂不是无论参考什么平面,到了变压器的前级都会出现阻抗不连续?

没有悬空的吧 从来没见过 肯定是接电容倒地 或者接电源的 这两种情况 虽然后者没有前者好,但 阻抗仍然是在可接受范围内的 ,如果你悬空 这个我还针没仔细考虑过 应该不行吧 可以测试下不过。