问题求助!

时间:10-02

整理:3721RD

点击:

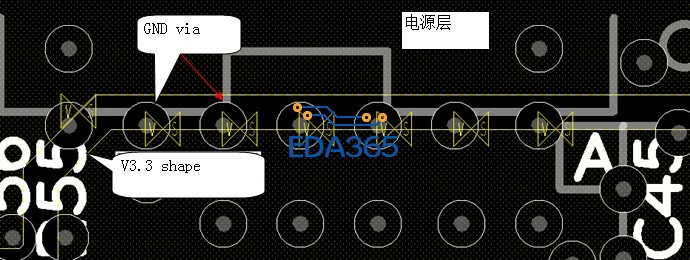

电源层3v3 的shape和GND的via 看上去已经短路了,这样在实际的做板的过程中有问题么?个人觉得没问题,因为GND via 有anti pad,所以shape在那个地方应该是被挖掉了吧?

电源层是正片的话这样是短路的,负片应该是没问题的

改成动态就行了

.........如果你的网络表示是没问题的,当然也应该是没问题的,那么大的DRC错误,那就是短路了撒。

如果要用静态的铜皮,也应该在PCB处理完成后再从动态转为静态,而且PCB完成后一定一定一定一定要检查status里面的项目,全绿才可以发板,当然有时候由于结构其他原因允许存在几个确定没问题的DRC。但是你这个图里面的绝对是不允许的

把光绘导到cam里面就一目了然了

这就是正片 负片的问题 如果你要正片就修改你得叠层里面

其实要是动态铜箔 就在点一下过孔就OK了 静态就转换下就可以

如果电源层采用负片形式,那就应该没有问题吧。