Allegro 同一网络的铜皮与过孔不连接的问题

时间:10-02

整理:3721RD

点击:

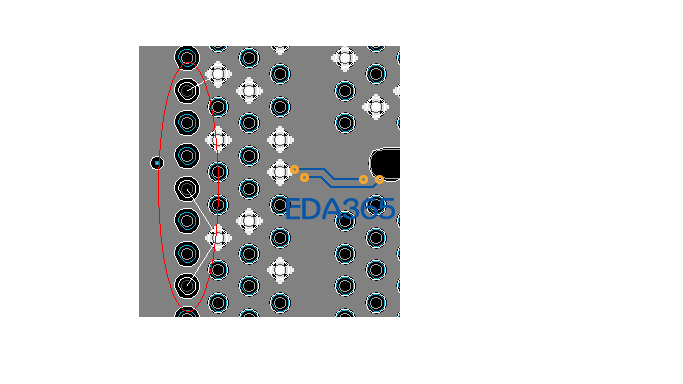

用Allegro 画PCB,分割电源层后发现 VCC3V3的通孔和VCC3V3的铜皮不相连,这里过孔设置是没有问题的,铜皮也是动态的。

如图,请教大家该如何解决!

如图,请教大家该如何解决!

可以修改铜皮的属性,应该是属性里面有一个连接方式你没有选对。

非常感谢,但能够讲的更具体点吗,是哪一个属性,我被这个问题折磨了好久

如下图所示

按照楼上的操作了一遍,结果还是一样,铜皮和过孔还是连不上。

看看是不是过孔设置了no_shape_connect属性

有几种情况!第一铜皮属性没设置好 UPDATA SHAPE 跑一下DBCHECK 第二 是全图都是这样还是只是BGA里面 同名网络 的设置问题

我也碰到这样的问题,有时候也跟抽风一样.

有的时候修一下铜箔,或跑下DBCHECK就好啦.有时候怎么都不好.

有没有找到问题点啊?我还是遇到这问题,是不是软件BUG啊?只能手动连接了。

学习了!等待求解!