BGA下这样走信号线好不好?

时间:10-02

整理:3721RD

点击:

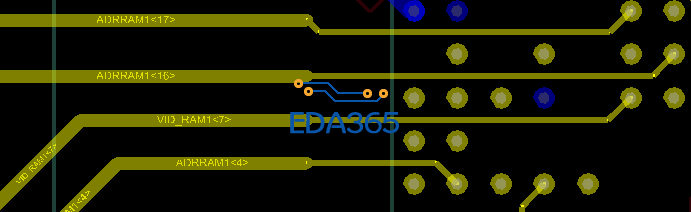

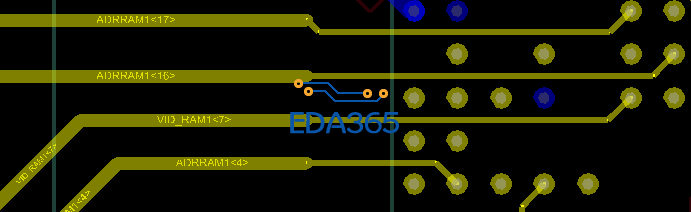

试着用Constraint Region在BGA上画了一个设定区域,在此范围下的走线由默认的12mil变为6mil,请问这样走信号线好不好?

可以这样,但是不明白你的内层走线什么要这么粗,6mil不行么?

我在设定Constraint Region时选的是“ALL”,就是所有层都这么走,感觉好看点

为什么不全部走6mil?

理论上来讲这样会引起信号的反射,不过实际中也经常会这样处理。

要是没有阻抗要求,线宽最好还是一致比较好

bga出线6mil的线宽,BGA下面一层要是地层的话,厚度是4mil,这样单端线就能满足50ohm阻抗了。线宽就不存在突变,从而也不会带来阻抗不匹配的问题了。

凡是阻抗不连续皆有反射。

問個題外話

如何能像開板大一樣線路上有 net name?@@?

我這請人layout的cpu

bga 下面頂多3mil轉接4mil

你一下線寬跳太多應該會有點問題吧@@

16.6版本的可以显示netname。

主板里面都这么干的