spi挂载多个设备,布线的处理方法

时间:10-02

整理:3721RD

点击:

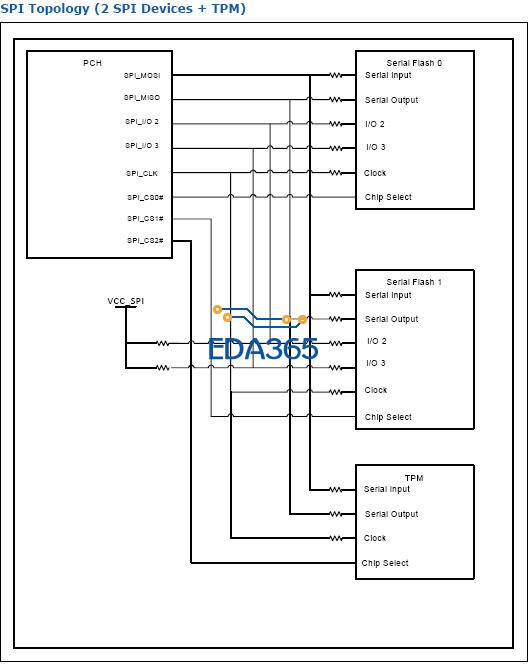

大家在spi总线上挂载多个从设备时,布线需要做拓扑结构吗?线宽 线间距 单端阻抗控制在多少为宜?大家有没有好的建议?

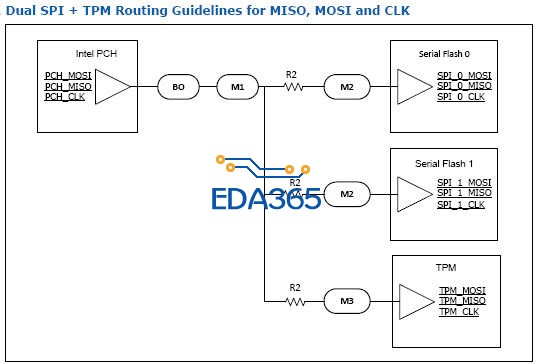

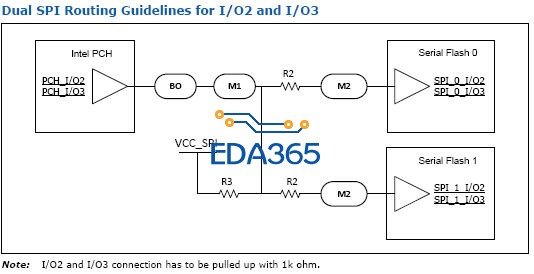

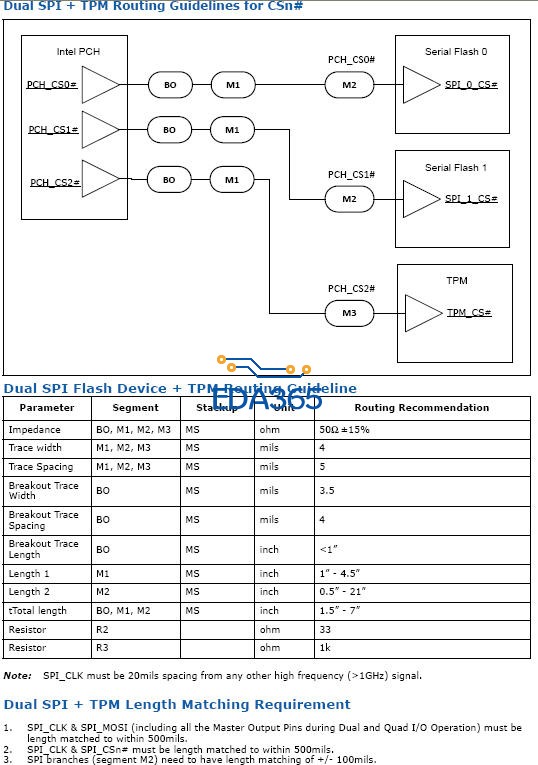

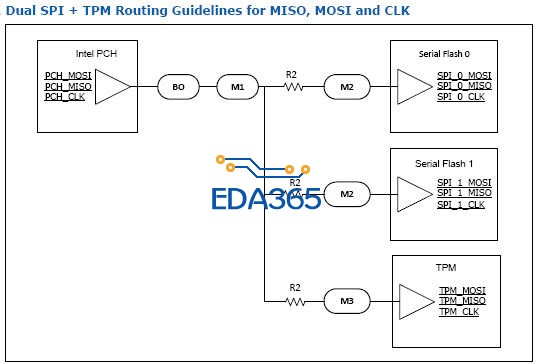

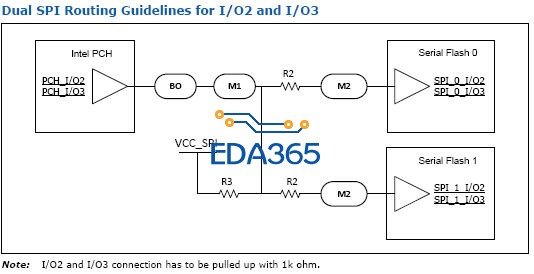

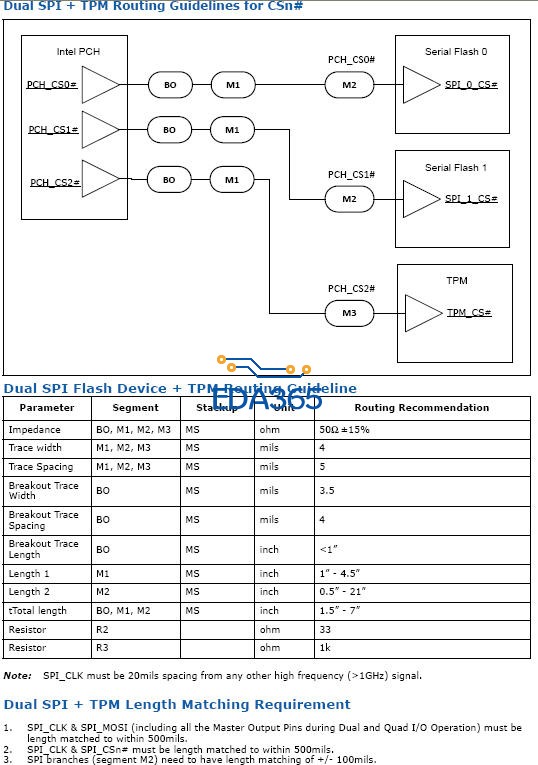

参考Intel的要求如下:

谢谢你的回答,我想想问问 pcb布线的时候要注意哪些地方,spi总线线宽 线间距 阻抗设置多少为宜? 总线走线要不要特殊设置什么?

线宽、线距、阻抗表格里面不是都有吗?备注里面还写明了等长关系。时钟线的间距走大些,其他都没什么。

非常感谢 你的帮助,从这个图上来看,我还有一点不太明白,BO是什么意思呀 ?是breakout trance (断点线吗?) M1 和M2本来就是一条线呀?为什么要分别设置呀?匹配电阻r2 r3的位置有要求吗?是在主机附近好点,还是在从机附近放置好点?

M1 和M2本来就是一条线呀?为什么要分别设置呀?对于这点我也不明白,希望帮忙解答下

这些资料都是在哪找到的,为什么我用的cpu资料里面都没有这些说明呢?