插件原件的地脚间隙加大

时间:10-02

整理:3721RD

点击:

各位大侠:请指点一下,关于插件原件的地脚间隙加大问题。

插件原件,比如:USB插座,4个引脚,我想把第四脚地在铺铜时,与动态铜的间隙远一点,其他的3个引脚不变,需要怎么设置。

插件原件,比如:USB插座,4个引脚,我想把第四脚地在铺铜时,与动态铜的间隙远一点,其他的3个引脚不变,需要怎么设置。

可以的。

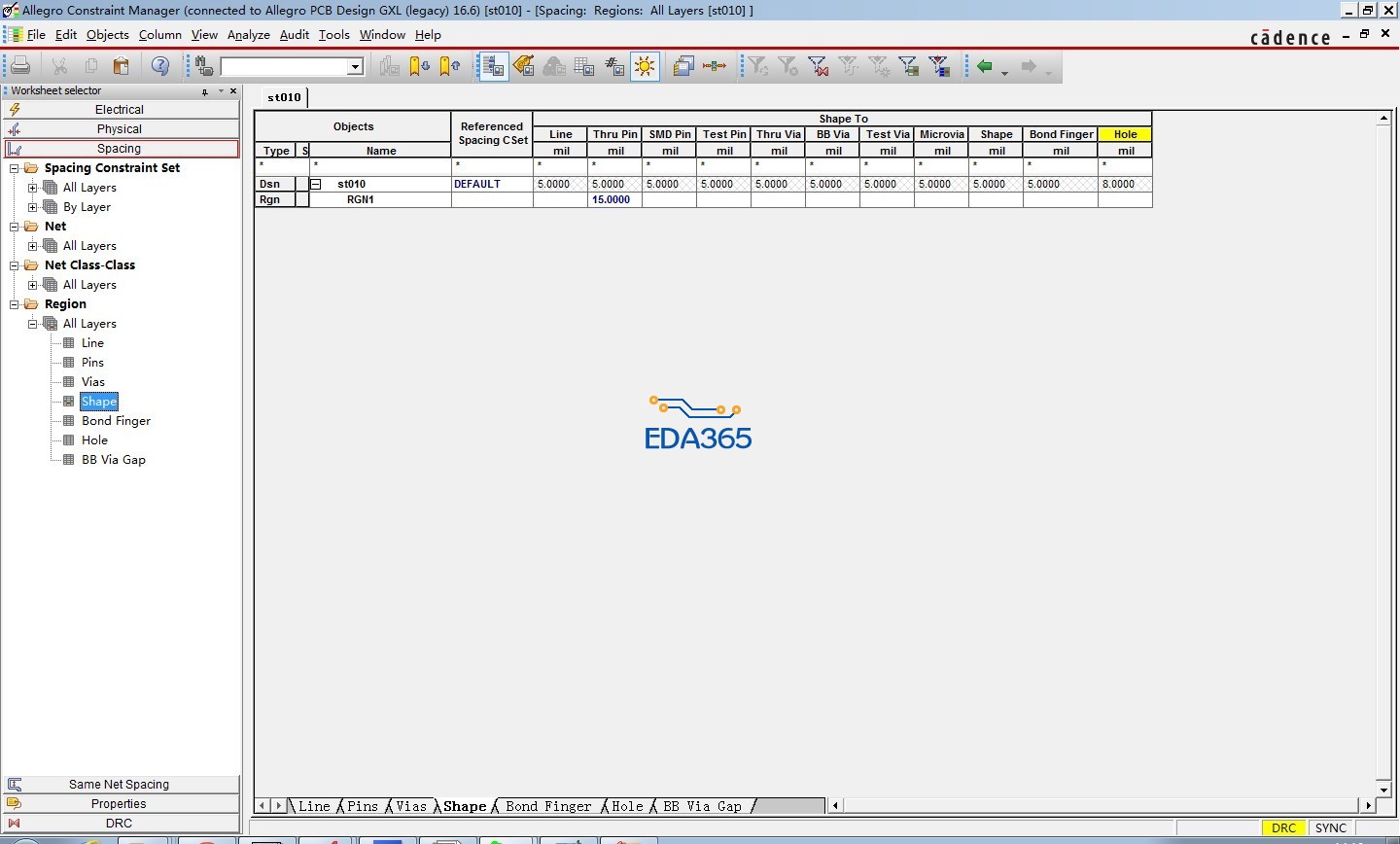

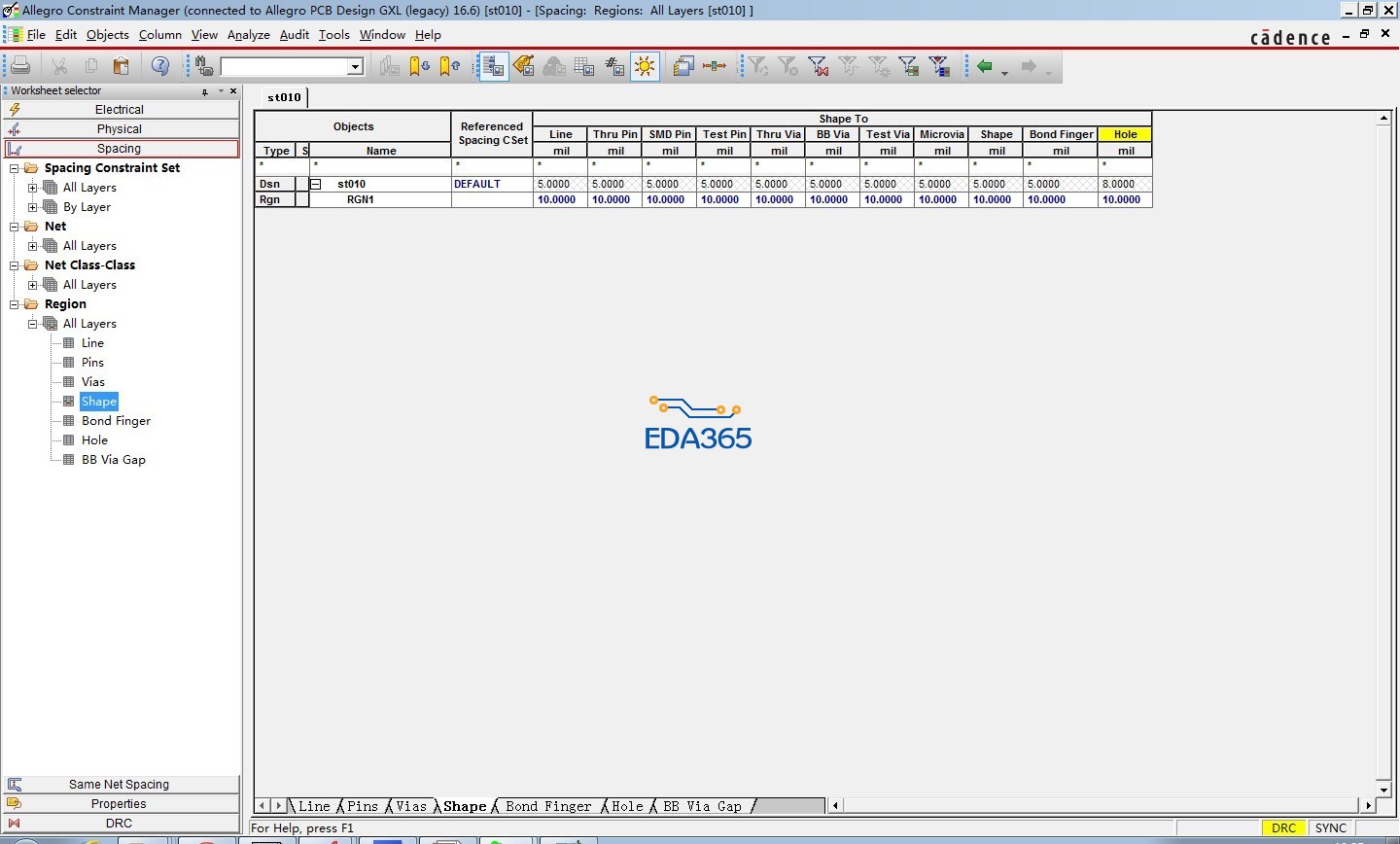

举个例子好了,比如说你现在是间距5个MIL的,第四个引脚的地方要加到10个mil

打开CMG,创建一个region 把你shape to thru pin的间距设置成10mil,关掉CMG。然后在constraint region 那个subclass下铺铜就可以了

以上小编:请问还的在PCB内创建这个区域,是怎么创建的,创建还,还要分配。还望详细的,谢谢!

小编只是想在那个引脚那边设置规则,对吧。

第一步,打开cmgr ,设置规则,简单点的话,就如下图

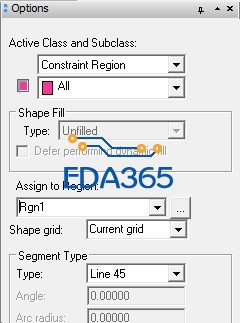

第二步,关闭cmgr,然后shape-->polygon,opition选项如下图,然后在那个引脚那边铺铜

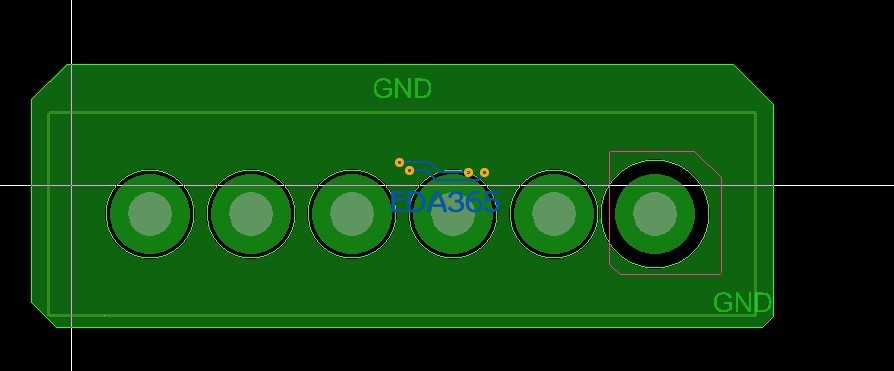

第三步,完成

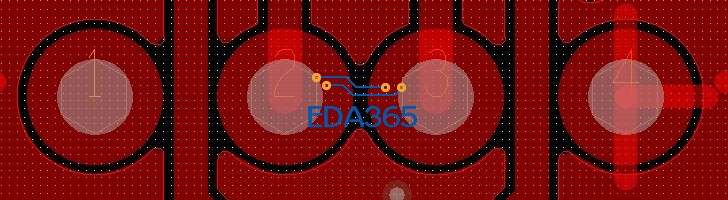

当然最简单粗暴的方法,就是自己手工挖啦