allegro 要复制一段线到新器件,为什么线放置后有DRC错误

时间:10-02

整理:3721RD

点击:

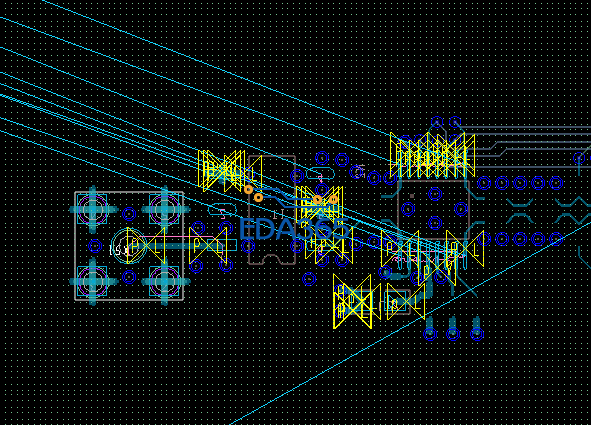

有二个完全相同的部分,一个已经画好,另一部分布局与第一部分完全相同,想直接从第一部分拷贝线,但是线放置到第二部分,连接出都有DRC,是不是复制的线带有第一部分的属性,如何复制,以及如何放置在第二部分而没DRC

还有如何精确控制放置线的位置

不要保留原来NET名就行了。你懂的。

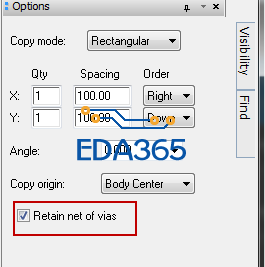

复制时,把图中所示的东西勾选掉 复制时抓住焊盘的中心 就不会出现DRC

你好,我用的是sub-drawing ,没有这个选项,在不同工程中还可以用那些方法拷贝图(不同版本),还有如何抓住焊盘中心精确定位?

谢谢

用这个subdrawing的时候是会出现这种情况,其实也算是线属性的问题,一般在拷过来的时候是dummy net,是线没有属性,与有属性的pin挨到一起了就会报错了。这种情况下可以动一下线就行了。但是我觉得用placement edit比较好用,先点击placement edit在find中勾中symbols->选中部品->右键单击place replicate create 输入x 0 0 选中点,然后就出现一个对话框,保存成mdd文件,然后再用同样的方法对新的模块使用这个命令是place replicate apply 然后找到上面保存的mdd文件,应用就可以了。

不是可以直接将原来的设置成mode,再用application mode-->placement edit就可以么?

你用的是老办法

能说一下具体步骤呢