如此诡异的DRC错误,求大神指教

时间:10-02

整理:3721RD

点击:

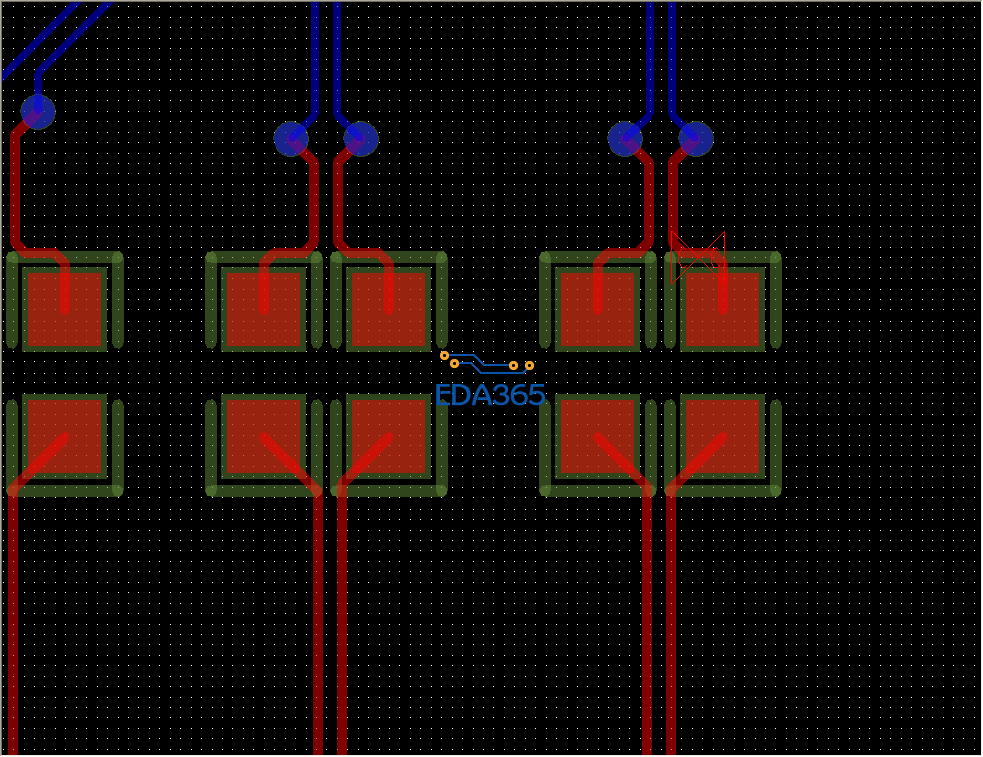

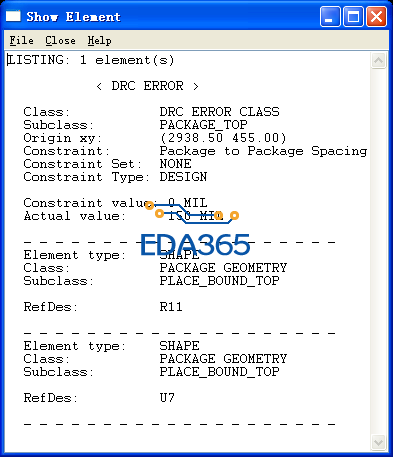

如图,左边的一对电阻完全正常,而右边的一对电阻却出现DRC错误,显示的错误是:(c and c )package to package spacing;而左边的电阻对与右边的电阻对是封装完全相同的,同为0603,(这是什么情况,下层没有任何的走线):我查看了DRC错误,如图,求大神。

不好意思 各位,我发完图片后突然明白了,真是浪费时间啊

那就说说是什么原因呀,

两个器件靠的太近了

好像不是很近 可以不管

做的封装靠的太近,一般封装没问题,可忽约。

看起来左边一组和右边一组的样子、距离是一样的。右边距离近的话,那应该左边一组也会有DRC。还请LZ再解释下具体原因啊。多谢啦!

请LZ再解释下具体原因啊。我还是有点不太明白。多谢啦!

Place bound 叠到一起了。

assembly框叠一起了吧

上面也说了,是两个器件的place_bound_top靠近了,不是那两个电容,而是电容右边的u7,一个max2,不好意思了,各位