Cadence使用心得,欢迎大家补充

最近用cadence设计了一块板子,用的还是比较顺手,但是仍发现有些疑问,欢迎高手指教。

1、在布完线铺完铜(dynamic shape)后,如果再调整布线,电脑会反应很长时间,甚至不能用slide工具,需要删掉原来的布线,重新布线。

2、在display里设置了no_shape_fill不显示,怎么再设置不显示铺完铜的边界以方便查看布线?

3、在更新symbol后,选中更新焊盘,为什么会和更新的焊盘有关的连线会不再连接,而是变成了飞线?

4、这个是关于添加测试点。想问一下,这个添加的测试点是什么?会出现在最后的板子上吗?什么样的?和原来的的焊盘和过孔有什么关系?不添加可以吗?这个测试点和不塞绿油的过孔什么区别?

5、关于差分线。差分线的uncouple length 什么意思?一般设置多长?对差分线有什么影响?

6、过孔需不需要soldermask层?

7、在画Anti Etch的时候,如果点击done之后再怎么修改anti etch 线?(我每次都是重画的,不知如何修改)

针对以上问题,希望高手指教!谢谢!

更新中。

欢迎大家补充,一起谈论一下用cadence时遇到的问题,分享一下自己的使用心得。

1.在动态铜皮属性里把铜皮Dymamic fill改成disable后再slide等操作。然后再改回smooth,这样就操作就比较顺畅。

2.不显示铜皮边界,那要看你用的是哪个版本。16.3以后的才可以。

3,我都是在板子上改焊盘,不是该封装,因为改封装就会出现焊盘连接的问题还要手动连接。

4.测试点就是在调试或者维修的时候测量关键信号用的。不盖绿油。

5.差分线的uncouple length 是差分线不耦合的长度。 差分线不耦合长度当然越短越好。但是在等长和耦合不能兼顾时就要选择等长了。

6.正常情况下一般的过孔要出阻焊层的,要盖绿油的。

以上是我个人见解,仅作参考。

简单回一下你的其中几个问题哈:

1,可以先设置全局的铜皮参数,改为disabled,这样就会快一些,特别是大板;

3,你哪个版本?16版本更新器件的时候,下面有几个选项,试着去勾选一下,另外可以把走线抓起来再原地放下即可,首先确保你更新的盘跟原来的盘中心是在同一个地方;

4,测试点是做DFT测试用的,一般是在加底层,也有加在双面的, 盘一般大小为30 , 32 最小可以为25。 可以添加的时候直接替换原来的过孔,如果需要添加测试点,那首先你打孔的和布线的时候就需要考虑测试点要求,不然布线完成之后,再来考虑,可能就加不上多少了, 有些板子要求覆盖率达到90%以上。 测试点的孔肯定不能塞绿油,不然怎么测试?

5,就是差分线没有偶合的长度, 一般设置需要看具体情况了,板子上有些是没有办法让差分走在一起的,如在小间距的BGA里面;

6,正常需要加上,如果不加,板厂需要多一道工序。

又学习了,感谢楼 主分享!

123点都不是问题, 是小编还不够熟或软件版本问题. 第4点,没加过.

16.3的,小编的第二问不显示边界要在哪设的能说下吗?谢谢啊

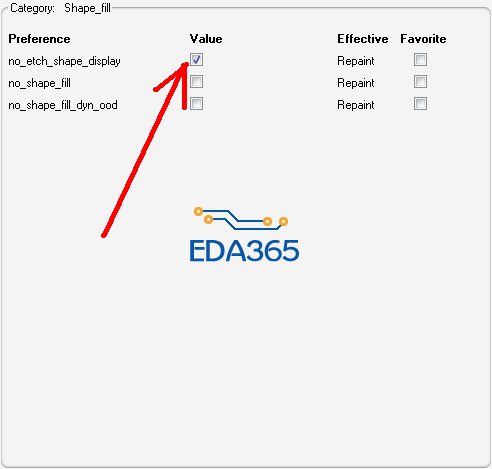

我的是16.6的,如图勾选。

谢谢啊,我的16.3应该没这功能的,没找到

16.3也有的,直接查询下应该就可以出来的

请问,这个在板子上直接改焊盘怎么改?

我是用16.5的,里面有这个选项,谢谢啊!不过还想问问你那个16.6的是怎么破解的?给个下载链接啊!让俺也尝尝鲜,嘿嘿

1、你说的第6项有点矛盾吧!?是不是过孔不应该有阻焊层,或者在出光绘的时候不出过孔的via class\soldermask层,这样就会达到过孔塞油的目的了呢?

2、顺便再问问,那个测试点是不是就是没有塞油的一般的过孔?

你说的那个测试点要求一般是啥?如果需要添加测试点,在打孔的时候应该注意什么?什么样打孔原则才能达到测试点覆盖率最高?

1,所有的信号都要打出过孔,包括表层直接相连的

2,两个也的间距至少50

3,离底层器件需要有一定的距离,具体可参考捷普的规范要求

谢谢!