实现模拟地和数字地单点链接的方法?

时间:10-02

整理:3721RD

点击:

大家好

我现在有这样的一个问题,

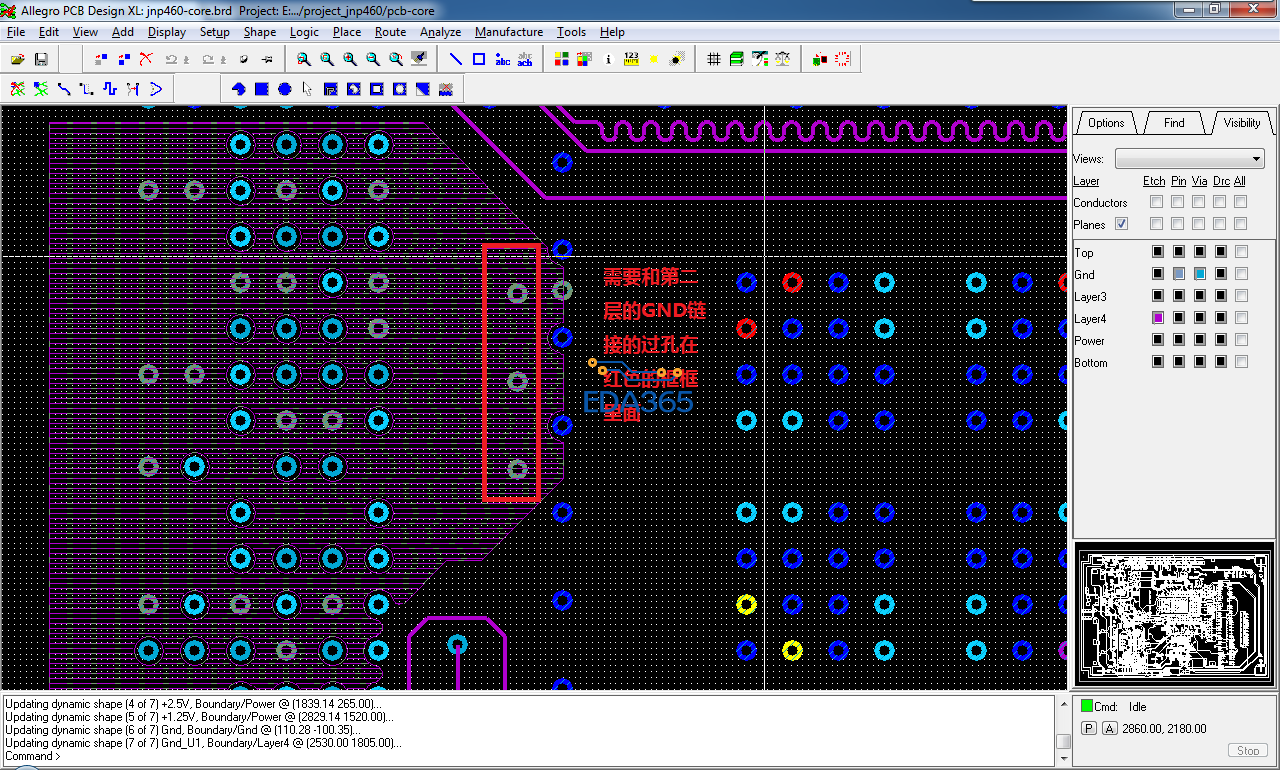

板上有数字地(GND)模拟地(GND_U1),内层2走的为GND,在别的层铺有GND_U1,现在想把这两个网络不相关的层通过过孔链接起来,

过孔应该怎么制作?

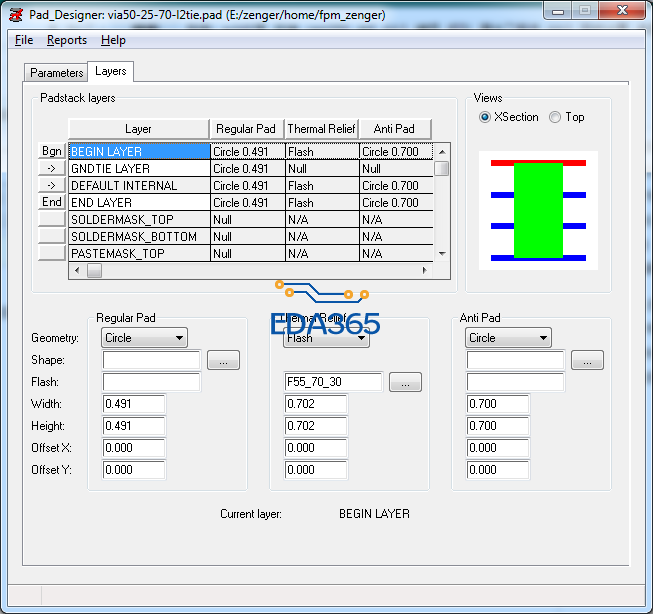

我本来是想把过孔加个 gndtie layer,在这个里面去掉 flash和anti ecth,但是我把这个做好的焊盘调到板上,anti ecth还是存在,不知道该怎么弄,以前看帖子的时候看到有人提过一次,不知道在哪里了

我用的那个芯片的demon板是用pads画的,它给加了个 ground tie layer,在这层里需要单点链接的过孔出拉了个矩形的shape,然后在出光绘是把这个加的tie层加入到了地层的光绘中,然后过孔焊盘全链接实现了GND_U1和GND的链接

这个方法我在allegro里面也试了,在board geometry里加了个gndtie层,然后画了个矩形,出光绘时也加到了gnd光绘层,但是没有起到预想的效果,anti etch还是把链接隔开了(使用cam350查看获知的),allegro 15.7,GND为第二层阴片

我直接在底层单点链接的过孔那里铺static的shape,然后赋值为GND网络都是被anti etch隔开的

不要建议加个电感或0欧姆电阻什么的来链接,不想这样做,就像能够直接链接

谁给帮帮忙,谢谢

按照个人看法:你可以这样做,从你的板子中炸出过孔的库,打开你会发现这个库在LAYERS这层里是按照你板子的叠层来填写内部层的,然后你就改里面的ANTI-PAD,然后保存成另一个名字,再在板子里添加这个特殊的过孔库,然后在需要的地方打这个过孔,试验过,可行,不知道这个 对你是不是对你有帮助

哈哈,哥们儿,多谢,已经按照你说的搞定了

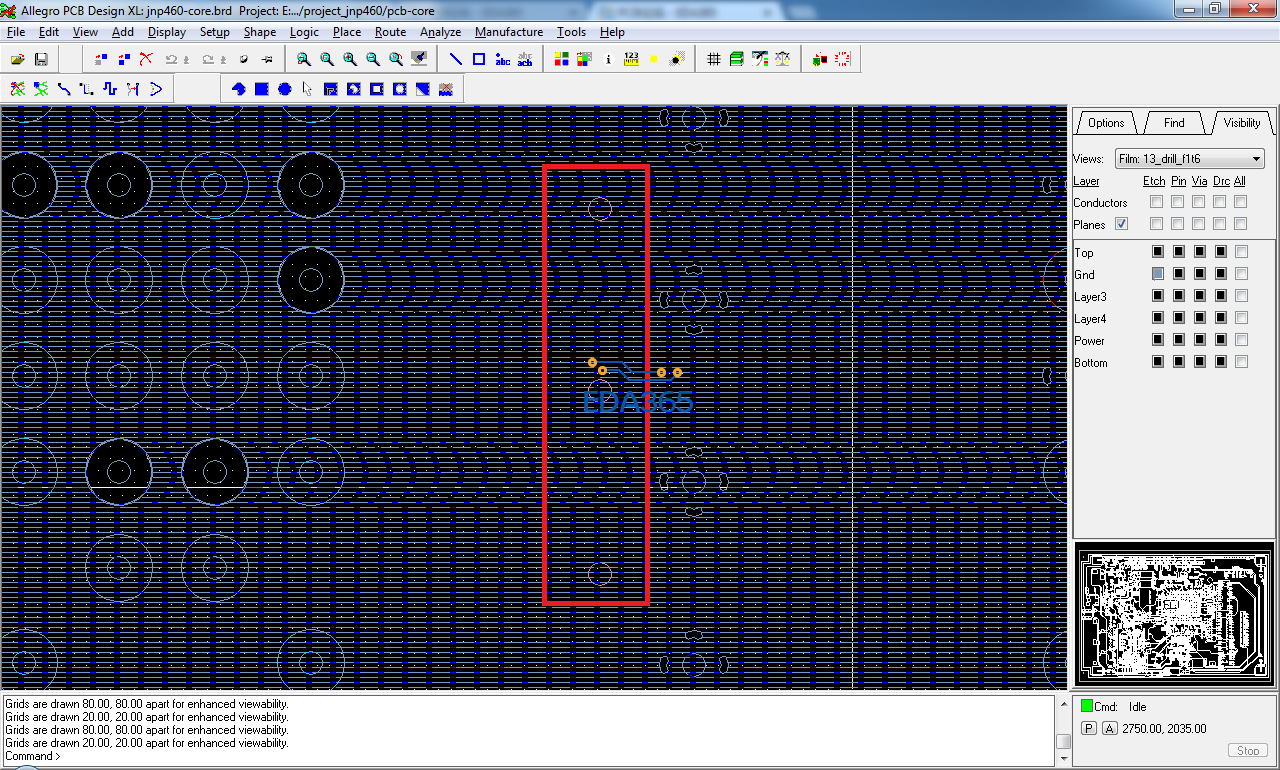

再增加一点,这个特殊的过孔需要添加 No_Drc 属性才能把 GND 层的drc报错去掉,去掉后就可以出光绘了,

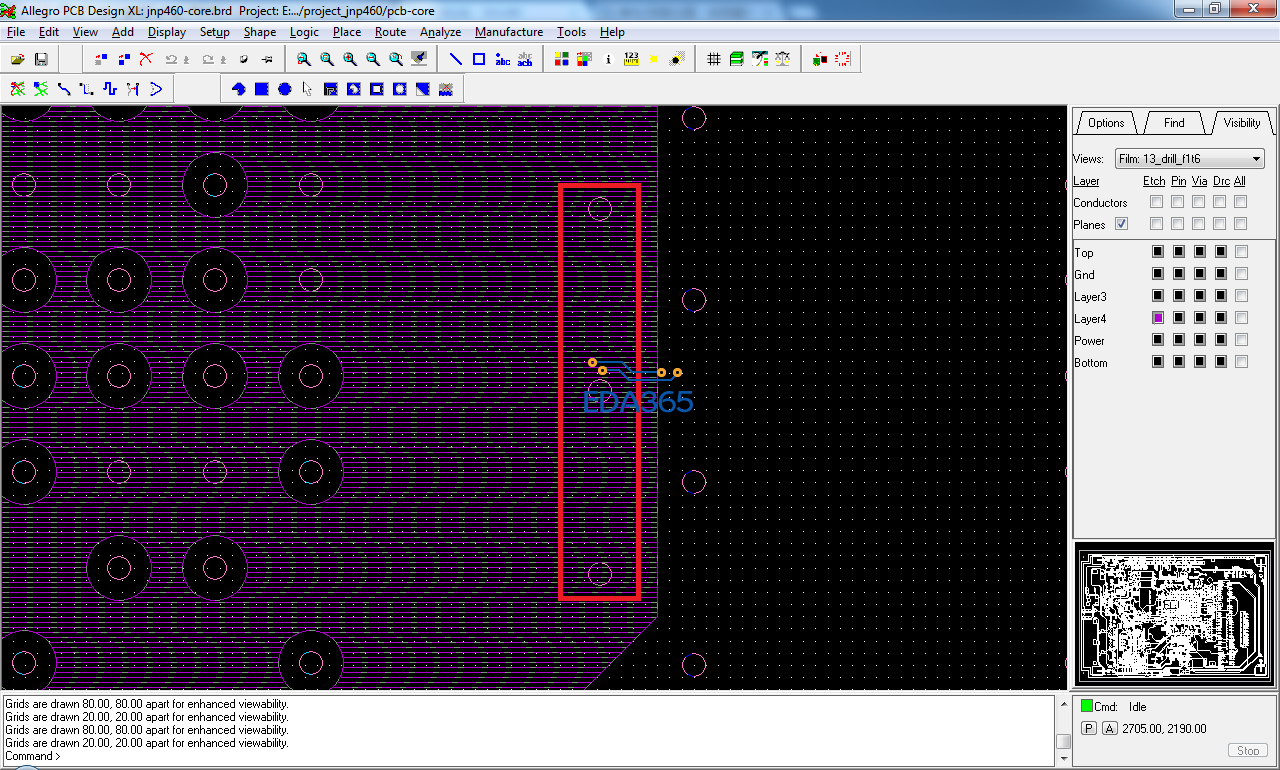

pcb图上和光绘的图上显示的都是正确的

在出光绘文件的日志(photoplot.log)里,关于GND层的警告也很清楚的表明了这个特殊处理的问题

有一点点遗憾的是不能设置为花焊盘链接,只能是全链接

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (331.96 3349.68).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (471.18 3349.68).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (500.00 3419.29).

- WARNING: Null ANTI-PAD specified for padstack VIA50-25-70-L2TIE at (2646.42 1997.50).

- WARNING: Null ANTI-PAD specified for padstack VIA50-25-70-L2TIE at (2646.42 2072.50).

- WARNING: Null ANTI-PAD specified for padstack VIA50-25-70-L2TIE at (2646.42 2147.50).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (5237.48 11.10).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (5307.09 -17.72).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (5307.09 179.14).

- WARNING: Null ANTI-PAD specified for padstack PAD_MTG300_700V at (5237.48 150.32).

第四层的GND_U1

第二层的GND(阴片)

不客气,共同学习成长