ALLEGRO中region设置无效

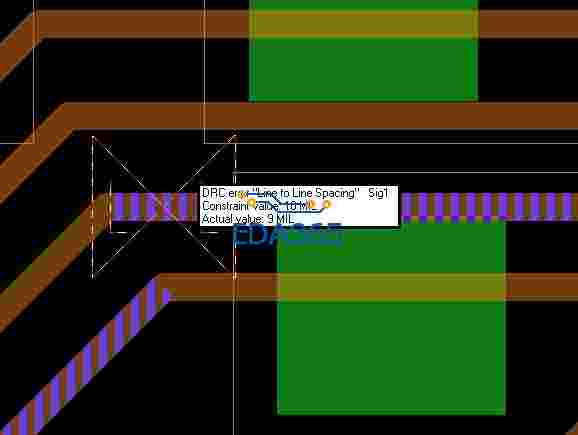

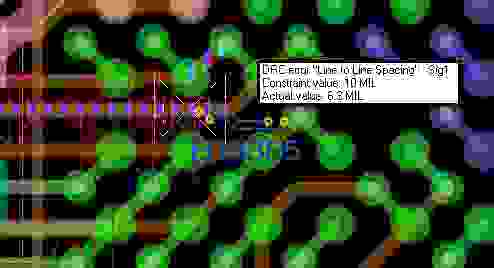

DDR2中数据线的net class设置的线宽是10mil,region中设置的region-class是4mil,当线宽是5mil时region中报错,是L-L的错误类型,即region-class中设置的约束根本就没有起作用。

把规则约束贴出来看下

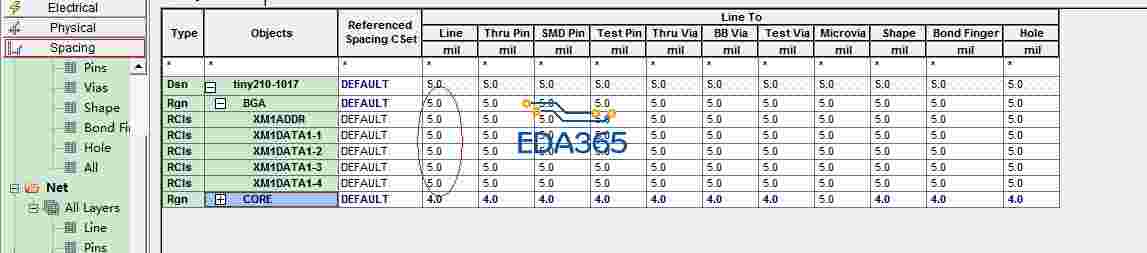

约束规则如下:

图1

图2

你这个报错是在region区域的边界处还是内部?

在region内的

我看了你的截图,你的错误提示是 constrain value是10mil,你实际只有9mil;你的region是5mil;region的优先级是高于net class-class的;9mil>5mil应该不会报错(前提是你的region设置没问题),所以你tools-update drc试一试,更新一下。

大侠,我的设置过程是这样的:

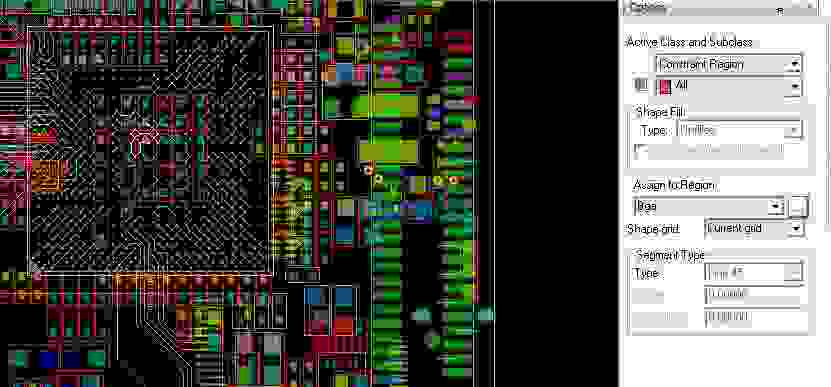

我建立的class(xmidata1-3) 中的线间距为10mil,如下图1.

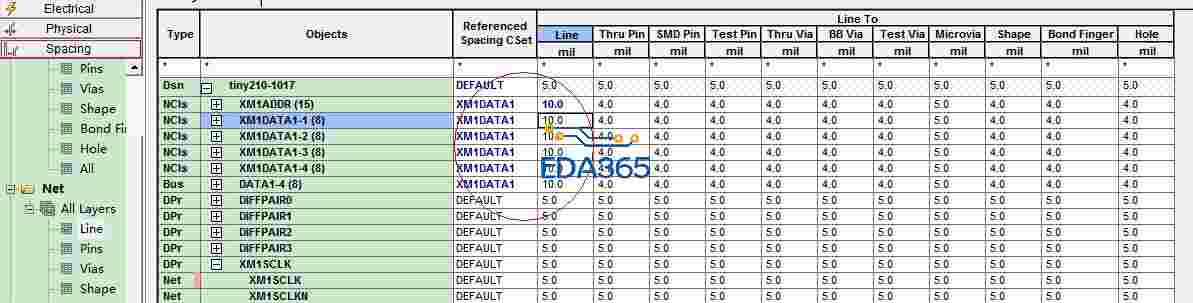

然后又建立了一个region(BGA),线间距的约束为4mil。然后再region下建立region-class项,线间距约束为4mil。如图2.

最后在我的板上通过shape-rectangular建立了一个约束区,并分配了约束,如图3.

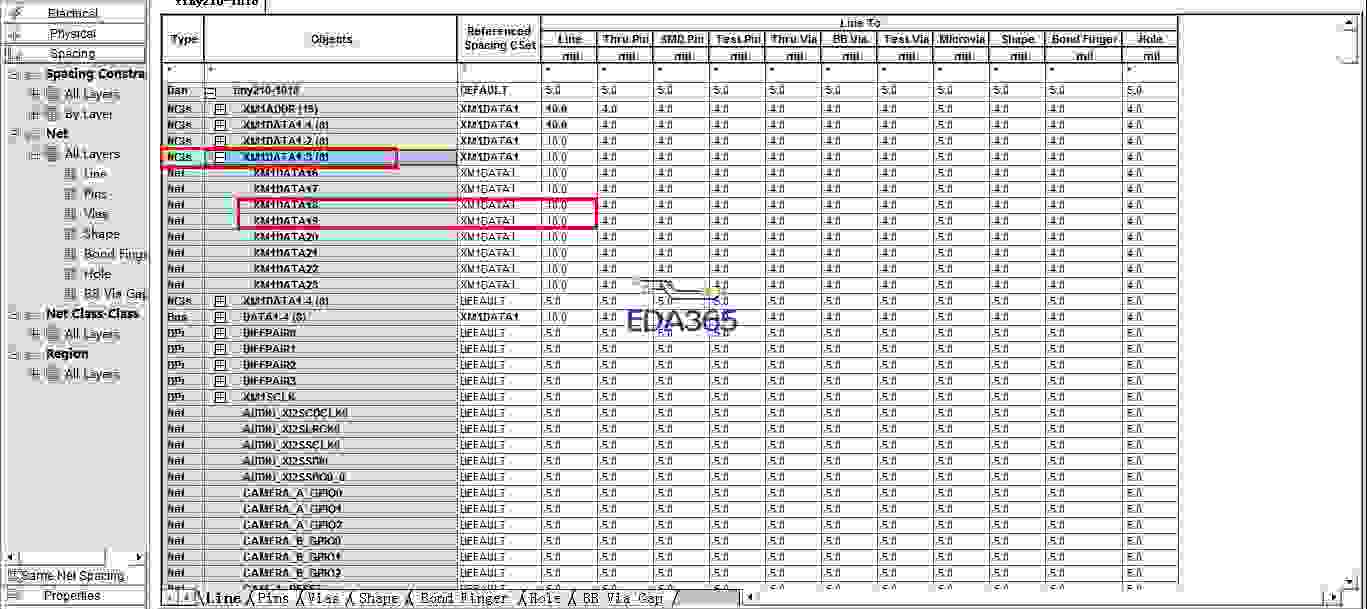

并更新了一下tools-update DRC,结果还是不行,如图4.

图1

图2

图3

图4

看你的出错位置似乎是在region区域的边界处呀,否则不应该是那根斜线跟横向的线报错,而应该是两个横向的线报错。

我确定是在region内部,并且报错的也有两横向线。

我知道是什么原因没有生效了,原来是在画区域之前就要指定约束的规则~~

差分对为什么在region中走线,region的规则怎么也不生效呢?

差分对的在PHYSICAL中设了NECK MODE值就好了

谢谢了~!另外设置constraint mode>physical mode>min neck width勾off,DRC就不显示了吧?

你这两个值设得都不一样吗 我一般在同一阻抗下这两个值设成一样的 呵呵