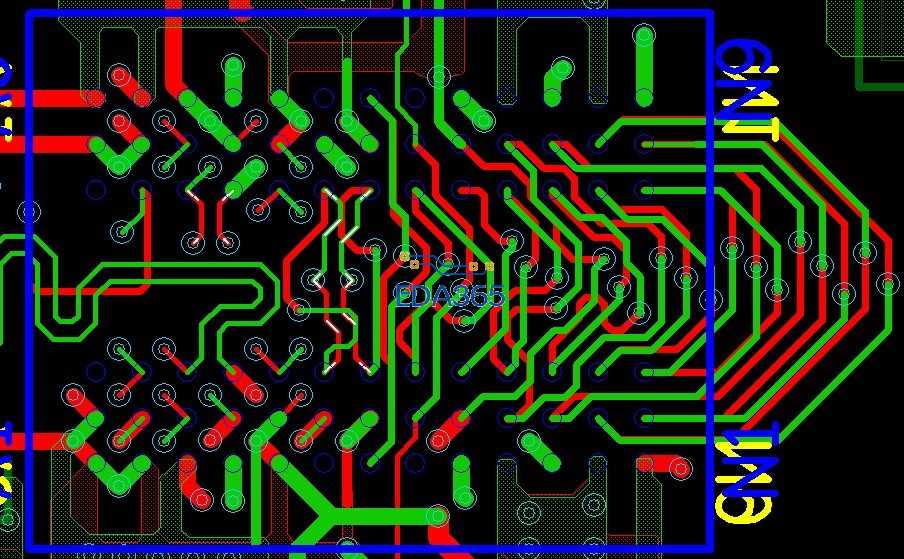

关于ddr3等长控制的问题,急!

8片DDR3,因板子空间有限,需要正反重叠贴片,即top面4片,bottom片4片,所以打孔非常受限。现在data线的等长已经完成,但是一片ddr中,最长地址线和最短地址线的长度已经差了1000多mil了,现在板子上没有太多的空间。请问地址线和clk等长最大可以控制在多少mil板子不会有问题?

我看您的問題覺得很奇怪, 請問您的 Constraint 是誰來設計的? 難不成是您自己隨手定的或是根本沒有規則可依據?

這都是有標準規範的 , 怎麼拉線會誤差這麼大.

就像二楼说的。本身规则就已经设置好了,在布线过程中会时刻注意线长问题。clk差分线与地址线组在1500-2500之间即可。

楼上的根据桩线定义似乎不应该超过520MIL吧?每组线间的线长,请问您1500-2500是怎么算出来的

这主要要看你ddr3的频率是多少,然后还有板子的介质,地址线之间相差不能超过波长的十分之一,比如说,ddr3的频率是300MHz,介质常数为4,根据波长=c/(f*根号下的介质常数),所以此时波长为3*10的八次方/(300*10的六次方*2),即为0.5m,所以布线之间长度相差只要不超过0.05m就可以,当然ddr3好像频率都超过800MHz了吧,你自己算算。

你这个计算方法仅仅是算出什么情况下,不用做信号匹配的方法。那个说1000-2500MIL是怎么算出来的?DDR3的主频应该在1333的,我只知道每组数据线间距离不能超过撞线定义所确定的,即不能超过上升时间RT,根据经验定理带宽等于5F从而可以算出带宽,在根据带宽=0.35/RT,算出RT,在根据RT算出线长,这里没有说时钟线和数据线的差距,如果有也仅仅是这里计算出来的,他怎么计算出1000-2500?我怎么算都算不出来,但是我肯定控制和数据是差我说的那个数字

我觉得他说的应该是错的,如果是1000mil,那就是25.4mm,对于频率超过1000M的ddr3来说相差肯定过大,这样的布线肯定是有问题的。

呵呵,另外我想问下,你的经验定理是哪里来的,一般是5倍f?那如果是4倍f,岂不是算出来的数据就不对了?

这个是正反完全重合贴啊,正反的地址线要连在一起,所以打孔非常受限制,连到主芯片的地址线只能按打孔的这个顺序连接,所以才会造成最长最短相差很多

地址信号比数据信号长1500-2500,是因为信号延时和地址信号电阻匹配等多因素。这个值是范围值,指导布线过程线长的要求。我一般布线的时候数据信号尽量短,保证地址信号大于1500即可,从来没超过2000。关于这个数值很多ddr3的文件说明都有。

学习

clk与地址线0.1ns以内,地址线CPU到DDR还要做T点,T点与T点的误差也好控制!

好奇DDR3的地址控制时钟不是走菊花链?

走在表面的線等長要縮短

介質不一樣

表層NET屬性速度比較快

感谢学习了!