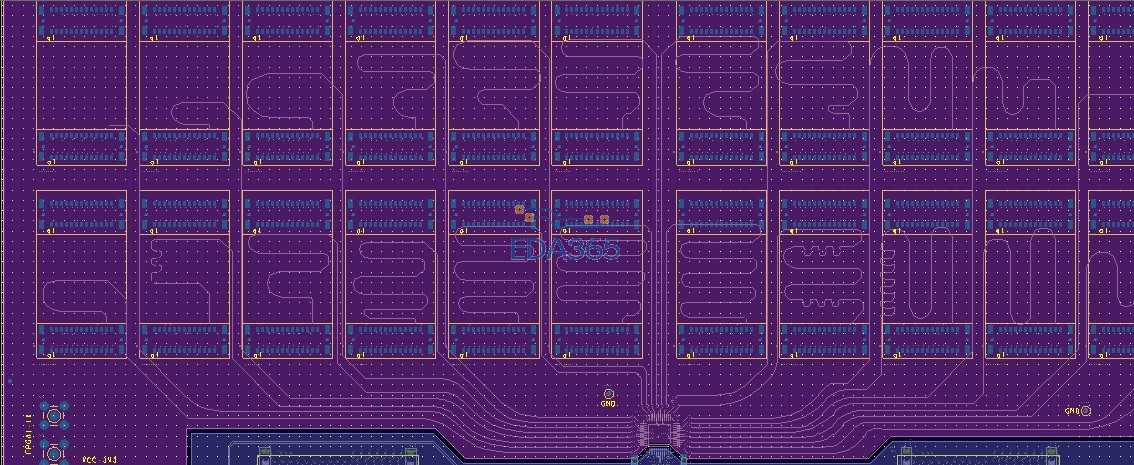

高速时钟分配电路及布线对电源分割的影响

请问有什么补救的措施吗?是不是倒数第二层分配成地层不会有这个问题啊?

1:加滤波电容

2:做信号端接

可以的话,平面做分割,模块间互不干拢。

以上建议,不知是否可以。

100M大概用多大的电容滤波,上过一个1nf的,没什么作用。

时钟分配器的输出都穿有电阻做端接,你所谓的“平面分割“是什么意思?我的问题就是这一大把时钟走线对相邻平面(紫色)分割产生上述”耦合“影响。

CLK 要给GND 参考平面 啊。

clock一定要给地作为参考平面吗?

反正我从来没有把clk,diff等信号参考过pwr层面

这个好像也不能说明时钟和差分信号不能以pwr层做参考吧

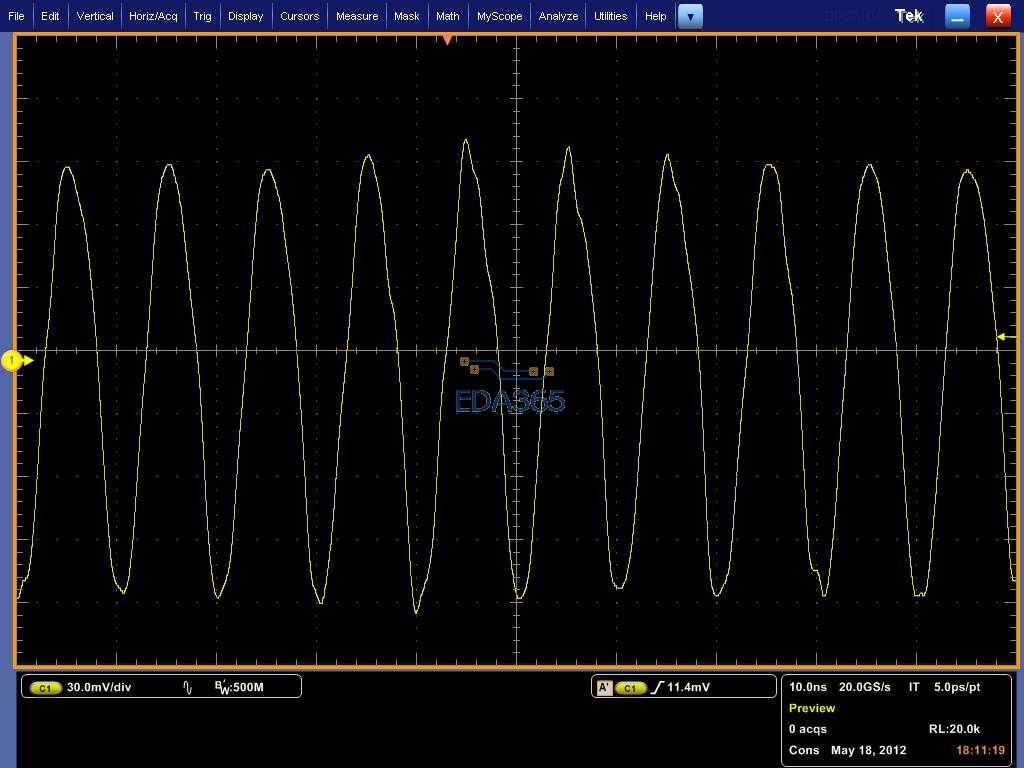

发现这个时钟分配芯片的辐射能量很大,探讨一挨近就能测到时钟信号

该时钟芯片摆在底层,时钟走线也布在底层,最靠近底层的内层是一个电源层,分割了不同电源,

那时钟走线有跨越分割线吗?如果说有的话,在走线旁边的电源层加电容试试(电容接在两个不同的电源区域)。

当时分割的时候也特别注意了这个问题,1楼的图片也显示了所有时钟走线没有跨越分割线

时钟是用紫红部分供电吗,有没有考虑过电源的驱动能力问题。

在时钟芯片的供电脚与地之间多加几个电容试,看有没作用。

虽然电源与地平面都可以作参考面,但用地肯定与用电源层来得好,特别是像CLK,DIP之类的。

现在板子已经出来了,说这些也没用,总不能等下版来证明这个问题吧,万一下版也是这样呢,最好还是找到问题的根本.

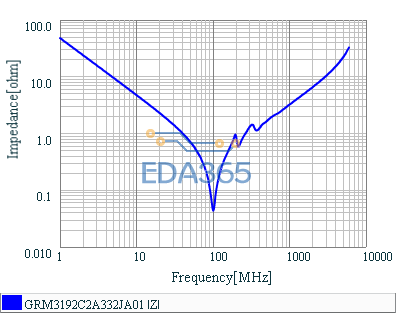

有没仿真过电源与地之间的阻抗是多少,最大频率是那一点,然后就多加几个电容将这个阻抗降到目标阻抗以下再试试看有没有效果。

3300PF在100M时的阻抗最小。

紫色部分跟时钟供电没有任何关系,我现在是把紫色部分的供电去掉,变成一个独立的铜皮后现象依旧。

现在将紫色铜皮独立以后,在铜皮和地之间加了一些电容,比如1nf,2.2nf,10pf各一个,现象依旧!

这个图的意思是否表示在紫色铜皮和地之间加一个3.3nf的电容?