关于芯片内部长度

2.不加这个长度影响大不大?

1.从芯片厂商而来

2.具体情况具体分析

做DDR,CPU用的多吧,其他的很少碰的到,以前作主板的时候是一定要加的,因为内部长度多的有1000MIL以上

知道了各个脚的内部长度,怎么加到cmgr里去呢?

INTEL 几个厂商的datasheet 里会有这个内部长度

不需考虑,这是制IC版图的人的事,制PCB版图的不必操这个心.

PCB设计要考虑芯片内部的等长问题,有些芯片做的并不是很规范,内部长度相差很多,这样的话即便外部进行了严格等长,还是达不到要求,pin delay的数据由厂家提供,有些芯片手册做的很好,在datasheet中就有表格,只需要把它拷到相应的.csv表格里就行,PIN dalay的表格格式如下:

REFDES 填写PCB板内相应的位号;

DEVICE 填写PCB板内相应元件的封装库名称;

下面左侧为pin number;右侧为PIN delay的长度;

表格制好后,存为后缀.csv的文件,或者从PCB中导出一个空的pin dalay表格,然后在表格中更改相应数据,因为曾经试验过,从.xls后缀更改为.csv,将表格导入PCB中,软件认不到,PIN delay并没有加入到相应的网络中去。

将Pin Delay的表格导入PCB的方法:

选择菜单【File】-【Import】-【Pin Delay..】即可

导出空的pin delay(.csv格式)的操作:

1、选择菜单【Edit】-【Properties】,Find选项勾选"PIN"

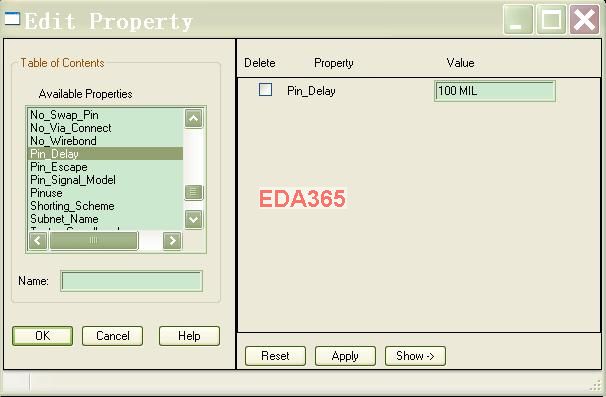

2、点击需要导入pin delay元件的某一个pin,弹出对话框,如下图:

选择属性PIN DELAY,在value里填写一个值,例如100mil;点击ok;

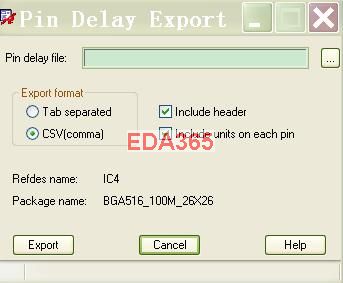

3、选择菜单【File】-【export】-【pin delay】,再点击刚才选择的元件,弹出如下对话框:

保持默认设置,点击Export,即生成.csv表格,然后在表格中更改相应数据。

谢谢楼上。学习了。

要求很高的主板要算的。记得曾经还是新人的时候。绕过的。

另外,表格导进去之后,在调等长时,需要记得勾选电气规则管理器中菜单【Analyze】-【Analysis Mode】中的option选项中的PIN delay,只有勾选了这项,在调等长时软件才会自动让pin delay加入到相应长度中。

我发的图你们能看到么?我怎么看不到,这个论坛上次发过图片后,很久没来,不会传图片了

亲,看不到图片

我也不知道图片怎么显示,两种方法都试了,都不能显示,我现在是以附件形式上传的,看能不能下载下来看?