在DDRII和DDRIII中 VRAM部分placement方式 利弊简谈~

时间:10-02

整理:3721RD

点击:

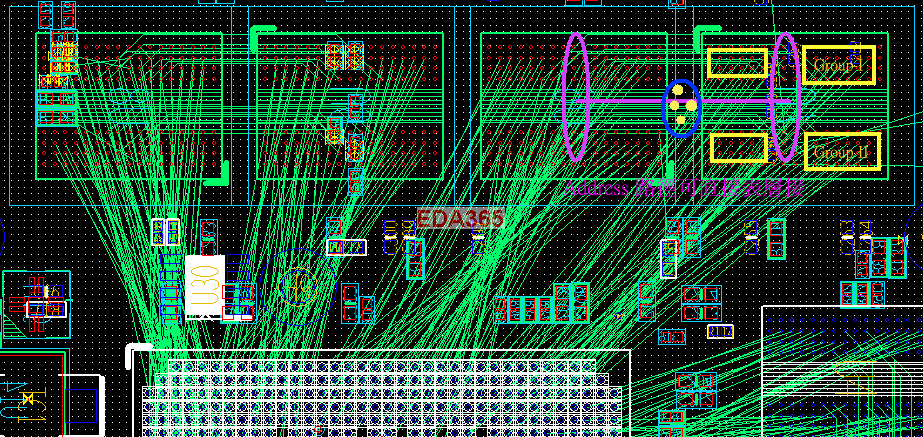

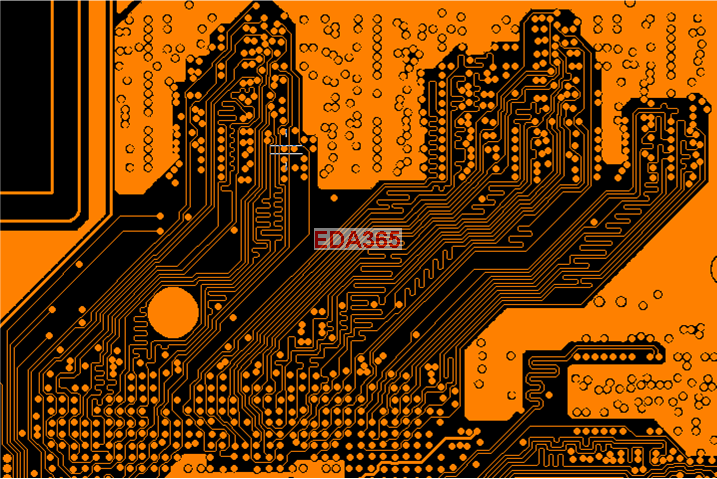

因為 VRAM BGA 的placement的不同,造成 layout 和 tune equal length 的难易度也会不同。在此show 出两种 placement的方式,供大家参考。 一、在DDRII设计中

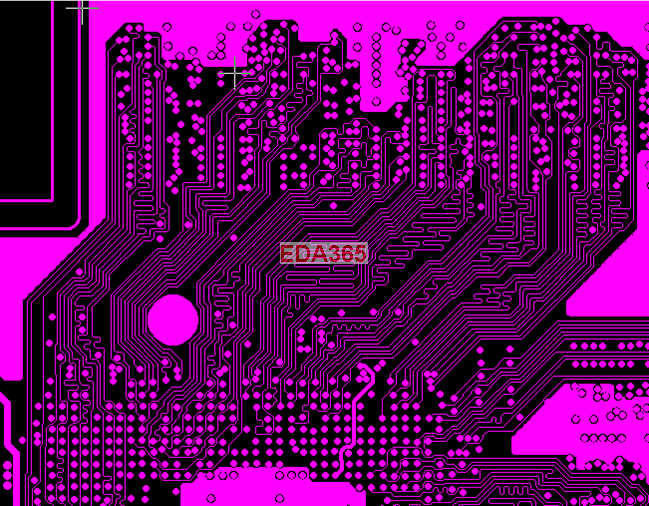

第一种placement 方式:

第二种placement 方式

总结:以上两种placement方式所佔据的空间大致相同,第一种方式在Y轴需要更多的空间;第二种方式则在X轴方向会佔据更多的空间,但它节省了Y轴上的空间。

在拉线方面,第一种方式data组内的长度相差不多,但group 与group之间相差很大(这点尤其在DDRIII时表现很突出);第二种方式 group 与group之间 的长度相差不大,但 data组内则相差较多。

而address也是各有千秋。因為DDRII的Address pin在小BGA的一端,因此第一种方式address的路径上不会有data挡路;而第二种方式则会必须从小BGA外面绕,但接小BGA的那一段可以直接用表层接,整段trace会小一颗via,少换一次层,且等长较好tune。

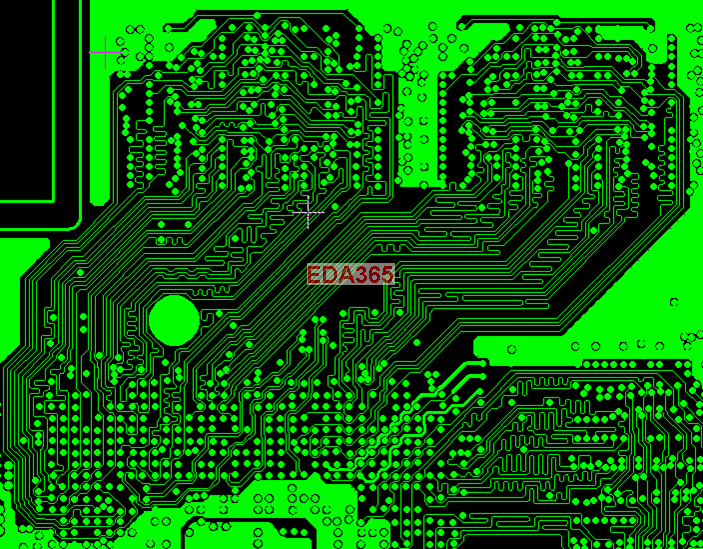

第二种placement 方式:

总结:以上两种placement方式所佔据的空间差别较大,但第一种方式在Y轴需要更多的空间;第二种方式则在X轴方向会佔据更多的空间,但它节省了Y轴上的空间。

这两种placement方式的最大差别还是在拉线和调等长的时候表现出来。

data 方面,它的pin define与DDRII是有区别的,整个Group是完全集中的。第一种方式Group I 与Group II的长度误差大概在800mil左右;而第二种方式可以减少这方面的局限。

addres 方面,第二种方式的优点更加明显,不但比第一种方式少一颗via,少换一次层,且用表层可以使两个小BGA 直接相连。且等长不用说也可以很容易做到。

如下图:

按照上图的placement方式,每个小BGA data中的三个group可以走在同一层,另外一个group 可以与address走一层。且等长也较easy!

也许,这对Cost down 来说是一个不小的福音!

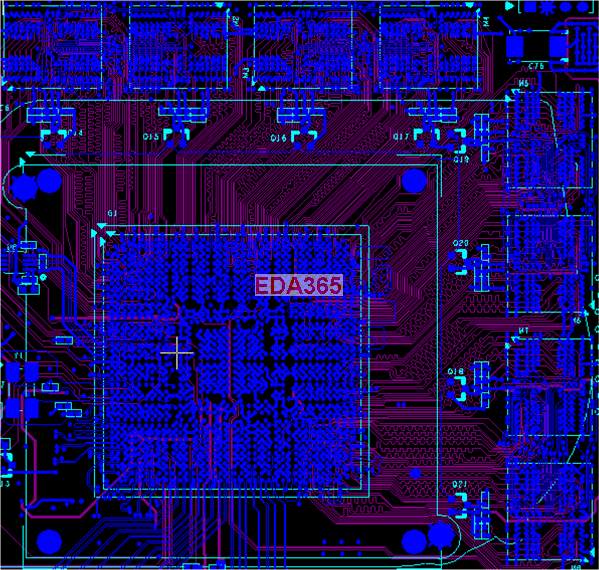

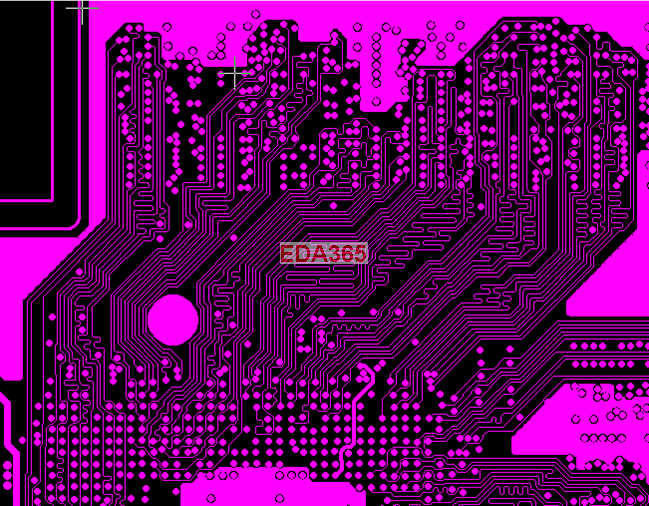

而第一种的placement方式,对拉线和等长都有不小的难度,用四个内层还走得那麼辛苦,

如下图

弦外之音,抛砖引玉:

GDDRIII共用Address和 Command的小BGA Data 可以swap,swap方式如下:

同一BGA的data group可以换,但必须保証DQS/DM的pin 互相对应。

同一group的data net 可以互换。

第一种placement 方式:

第二种placement 方式

总结:以上两种placement方式所佔据的空间大致相同,第一种方式在Y轴需要更多的空间;第二种方式则在X轴方向会佔据更多的空间,但它节省了Y轴上的空间。

在拉线方面,第一种方式data组内的长度相差不多,但group 与group之间相差很大(这点尤其在DDRIII时表现很突出);第二种方式 group 与group之间 的长度相差不大,但 data组内则相差较多。

而address也是各有千秋。因為DDRII的Address pin在小BGA的一端,因此第一种方式address的路径上不会有data挡路;而第二种方式则会必须从小BGA外面绕,但接小BGA的那一段可以直接用表层接,整段trace会小一颗via,少换一次层,且等长较好tune。

回复 天使旋律 的帖子

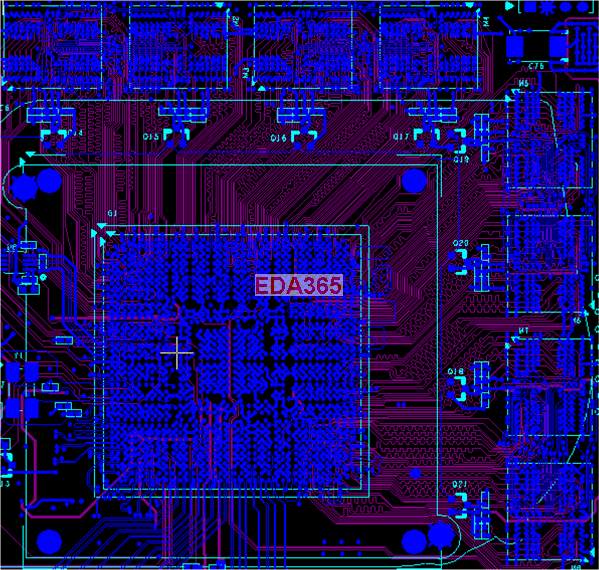

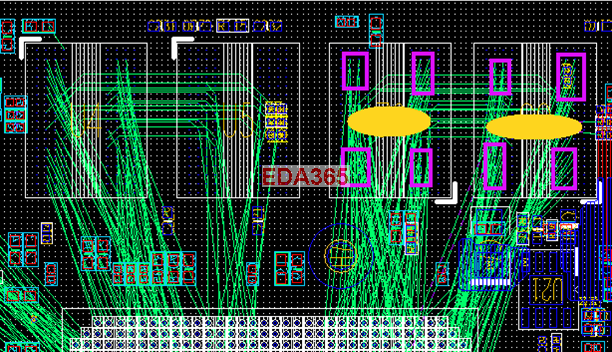

二、在DDRIII设计中:第一种placement方式:

第二种placement 方式:

总结:以上两种placement方式所佔据的空间差别较大,但第一种方式在Y轴需要更多的空间;第二种方式则在X轴方向会佔据更多的空间,但它节省了Y轴上的空间。

这两种placement方式的最大差别还是在拉线和调等长的时候表现出来。

data 方面,它的pin define与DDRII是有区别的,整个Group是完全集中的。第一种方式Group I 与Group II的长度误差大概在800mil左右;而第二种方式可以减少这方面的局限。

addres 方面,第二种方式的优点更加明显,不但比第一种方式少一颗via,少换一次层,且用表层可以使两个小BGA 直接相连。且等长不用说也可以很容易做到。

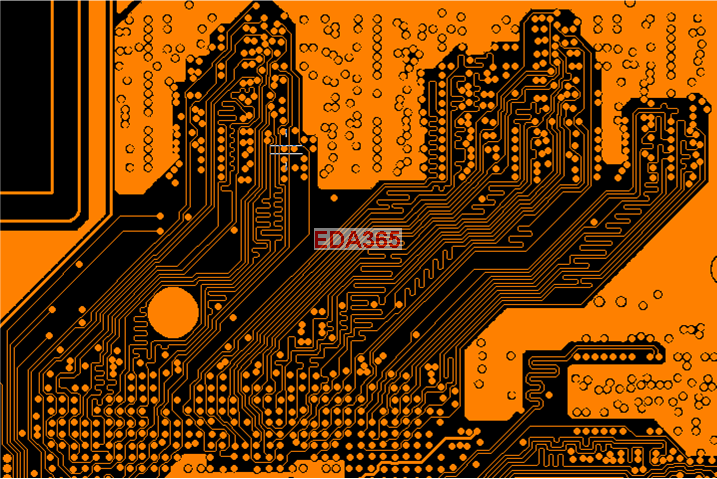

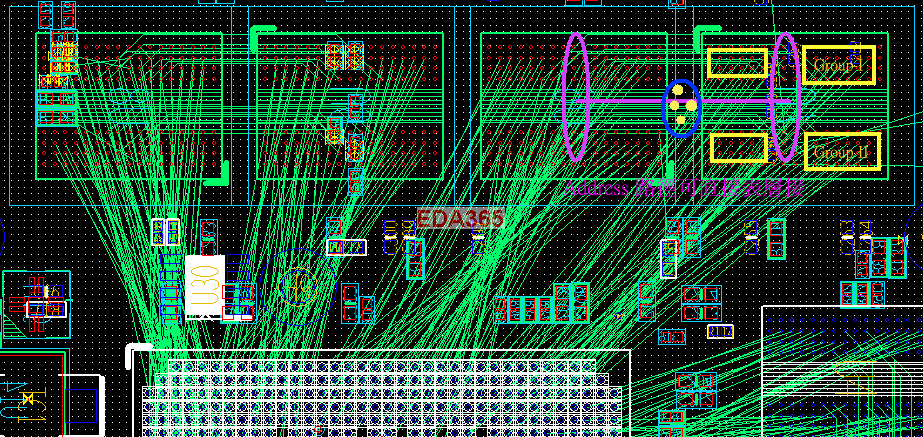

如下图:

按照上图的placement方式,每个小BGA data中的三个group可以走在同一层,另外一个group 可以与address走一层。且等长也较easy!

也许,这对Cost down 来说是一个不小的福音!

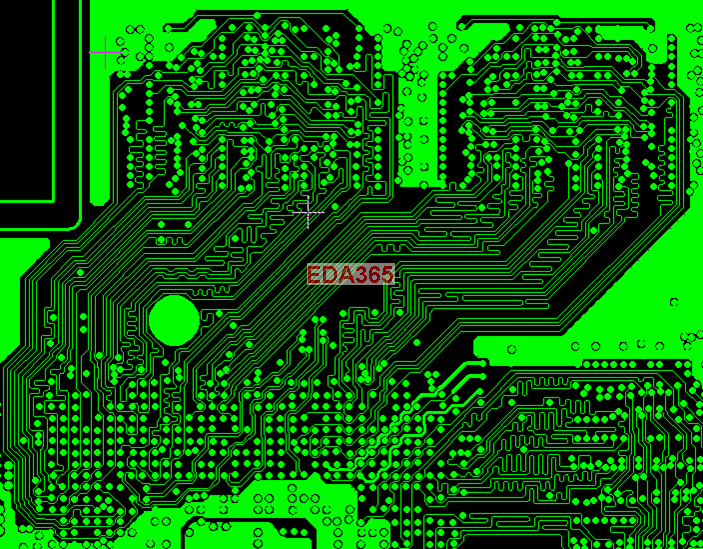

而第一种的placement方式,对拉线和等长都有不小的难度,用四个内层还走得那麼辛苦,

如下图

弦外之音,抛砖引玉:

GDDRIII共用Address和 Command的小BGA Data 可以swap,swap方式如下:

同一BGA的data group可以换,但必须保証DQS/DM的pin 互相对应。

同一group的data net 可以互换。

结论呢?

回复 wzh6328 的帖子

结论就是,在DDRIII元件的place,推荐第二种placement方式;至于DDRII设计,两种情况都有自己的利弊,看自己的想法了,呵呵~

LZ辛苦,很直观,很强大~

:victory:

LZ辛苦了

lz强大啊

不错

太棒了,最需要的就是这种复杂器件的place经验

不错.很有启发意义.

学习中,感谢小编分享

只要层数够,怎么摆都行

回复 CAD_SI 的帖子

呵呵,如果这么说,那么如果工厂不考虑亏本,买方不考虑消费,还用我们设计做什么?