重新导入网表后,shape的net属性丢失了,大伙有没有遇到这种情况?

时间:10-02

整理:3721RD

点击:

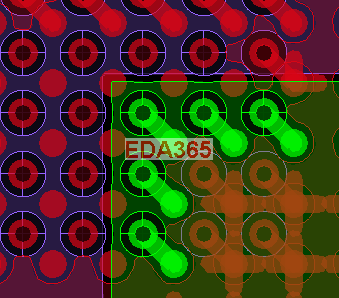

如题所示:导入前如下图

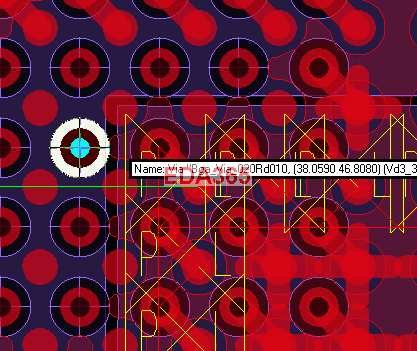

修改原理图后,重新导入后,

有知道这是咋回事?

回复 黑月 的帖子

找到原因了!

在修改前,原来的属性为VD1_2_FPGA,这是由于修改原理图中root页不当造成的!

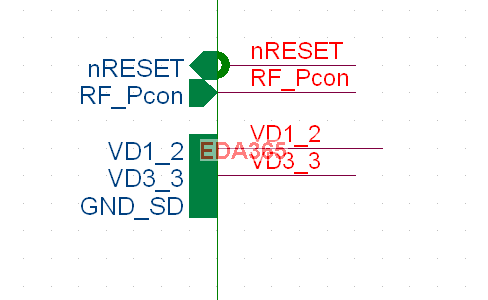

图1:fpga

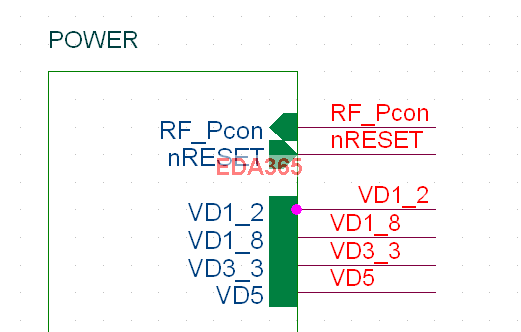

图2 POWER

修改前的toot页没有VD1_2;修改后,root的fpga层次块中添加VD1_2端口,但是没有添加POWER层次块,此时root的fpga层次块中添加VD1_2端口的net,会变为VD1_2_FPGA,导入网表,shape的net网络会变为VD1_2_FPGA。

等我添加POWER层次块,root的fpga层次块中添加VD1_2端口的net,会变为VD1_2!

修改办法:logic/net logic,把 VD1_2_FPGA重新命名为VD1_2

注意:

1、电源、地的符号的电气规则是全局的,尽量避免出现这些符号的端口!

2、orcad的net是自动生成的,先从root开始;为了移植方便,尽量手动拉一根线,然后添加net!

电源、地的符号的电气规则是全局的,所以可以不用加port!