Nvidia显卡设计中,多个显存CLK、CMD、DATA信号分段等长设计

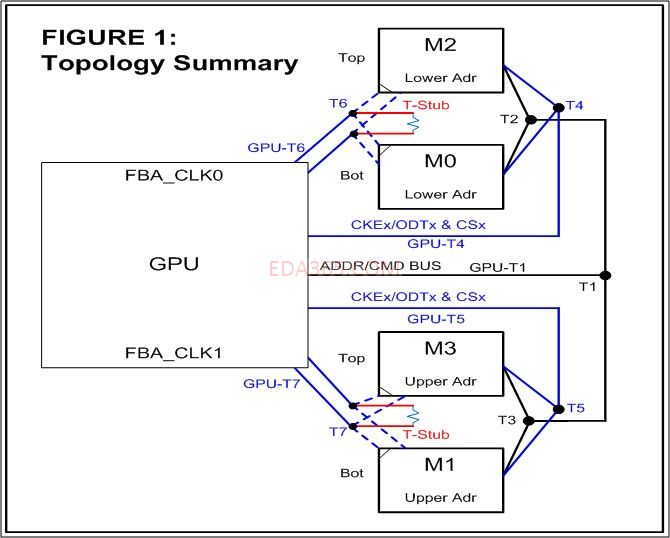

如图所示,NV显卡设计中,显存的信号需要做分段等长,要求不同信号的时延在一定范围内,因此需要把线长的mil转换为ps(皮秒)。此外,不同的信号间存在相互关系,如:CLK to CLK,CLK to CMD,CLK to CMD等。

CLK信号FBA_CLK0从GPU到M0与M2,T6为分叉点。GPU到T6为公共部分,在T6点分叉。

CMD信号更是1分2,2分4。GPU到T1,T1在分部到T2和T3,T2,T2再分别分岔到M0,M1,M2,M3。

每一段有微带线也有带状线还有via,而微带线与带状线的转换为ps的算法不同,还需要将via转换为线长计算。

NV有提供EXCEL表格,将每一段的线长填入表格,并检测线长是否合乎规范。而本人目前只能通过手动选取每一段Cline,并判断此Cline是位于哪一层,再根据相应公式转换为ps,在求和后将结果手动填入NV提供的EXCEL表格。对于8颗显存的多层板设计,每个项目都将花费数日来获取并填入数据,修改之后又需重复此过程再次检查。过程极为复杂繁琐。

因此,请问高手。

有没有办法,讲每一段CLine的长度report出来?并且获取via穿越叠层的信息?

或者,有没有办法在allegro中设置约束规则,以达到NV设计规范。

我也非常想知道DDR3的一些设计资料,特别是在计算T1\T2\T3的走线时不好算,不知哪位有好点的方法。

另外我是用PADS2007做这个设计,这工具不可以像allegro那样来设置T点,不好用,如果是用allegro就方便了很多。

希望有经验的高手们给点资料和方法给分享下,谢谢!

前公司的SI Team专门写了个Skill,就是导出等长线在各个层的长度信息的,甚至还能标注是Break Out/Break In/MS/SL等段信息,然后就可以对等长表去检查了。不过那skill竟然还要连接到公司服务器才能用,还有密码验证,现在连我都用不了了。

源码是加密过的,虽然没密码,不过解密后的可读性有点差,如果有高手读源码后又办法改写成本机可用的版本,我愿意把skill发上来。

我感觉这个网络验证本身并不提供什么功能,功能在脚本里都可以实现。

其实小编所说的工作,在前公司就是EE经常要做的等长检查,内容几乎一样,只是他们有脚本导出信息,自己要做的只是撰写表格,填入数据而已。

T点似乎只能以mil计算,这个需要换成转换为ps

skill似乎不错,研究研究。

兄弟,能否提供一下,我已经学习skill一天了。

如何让解密文件更有可读性, Pls go to http://www.eda365.com/wiki/Skill_Question/%E5%8A%A0%E5%AF%86%E4%B8%8E%E8%A7%A3%E5%AF%86 , pls changed eda365 to pcbskill.

加T节点,在control manger里面设置匹配规则就可以了

要注意T1和T2 T3 T4 T5的阻抗控制要求是不一样的

good, study

都是高人,学习了

\doc\algrologic\algrologic.pdf

有文档介绍,同学习。tks。

都是强悍的人

回复 st.liu 的帖子