请教:铜皮问题

时间:10-02

整理:3721RD

点击:

有块板子要修改,在修改中遇到下面的问题,请各位帮忙解疑:

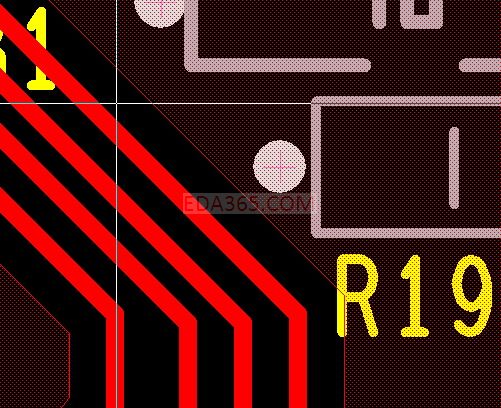

下图1是正常,同一层的走线和铜皮间有间距隔开的

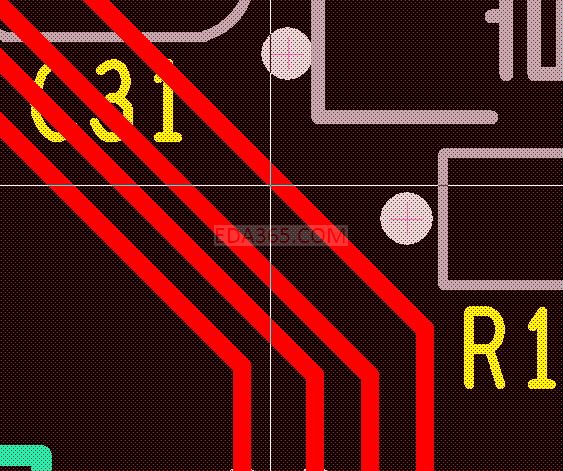

但是只要对走线进行修改后就成下面这样了,也没出DRC错误

哪位知道的告诉下,谢谢!

坐看真相..

我真不懂

铜皮删掉,修线后重新铺呢

是整块板子的铜皮都出现这样的问题,还有就是把一个网络拉到另一个网络的铜皮上,铜皮也不避开...

而且重新铺通也都一样...

把铜皮change一下到静态或者动态铜皮,一个回合之后应该就可以了

谢谢啊。原本是动态,改成静态的再改回来也不行,重新铺上动态的铜皮还是一样。整块铜全连一起,不会和其他网络避开....

虽然改成静态的可以手动避开,但想知道下动态为什么会出现这问题....

菜单shape-----global shape parameters-----clearances

看一下设置是否正确

谢谢,经你提醒,发现是shape-global dynamic shape parameters-shape fill 下的dynamic fill 选项选成"Disabled"弄错了,改选成“smooth”就可以了。谢谢啊。

学习了

学习了