差分3W规则求教

时间:10-02

整理:3721RD

点击:

求教,在cadence16.2中,差分线之间如何设置3W,而保证不报DRC。

现象:在16.2中,很多走线设置了差分属性,然后再想设置差分线之间遵循3W规则时,走出来的差分线就会报DRC,

就是说差分线对内的物理属性(线间距)与3W规则冲突。求解。

多谢多谢

希望大侠们不吝赐教·~

高速差分布线有的尽量靠近,这就不需要什么3W规则了。另外,对于高速差分布线,有两点要注意,一是两条线的长度要尽量一样长,等长是为了保证两个差分信号时刻保持相反极性,减少共模分量。另一是两线的间距(此间距由差分阻抗决定)要刻意维持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一层,一为两条线走在上下相邻两层。一般以前者实现的方式较多。等距则主要是为了保证两者差分阻抗一致,减少反射。对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗的值, 此值是设计差分对的重要参数。

谢谢你了,但是你所答非我所问~·~

我问的主要是规则设置,如题~

继续求解,希望有人可以帮忙,再次谢过

15.5中:

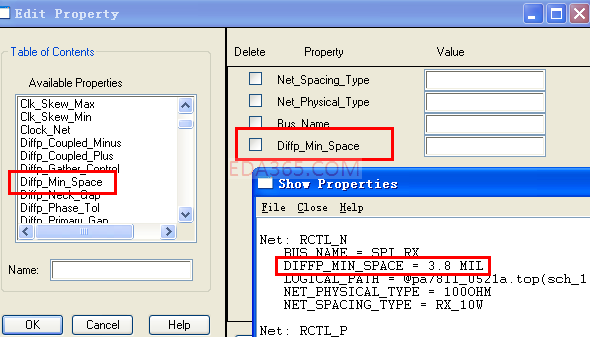

方法1、加上这个属性:

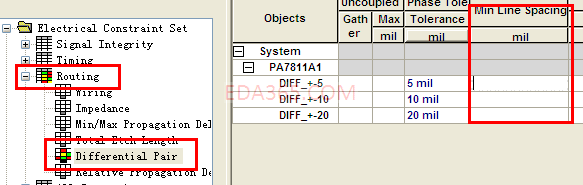

方法二、在这里也可以加:

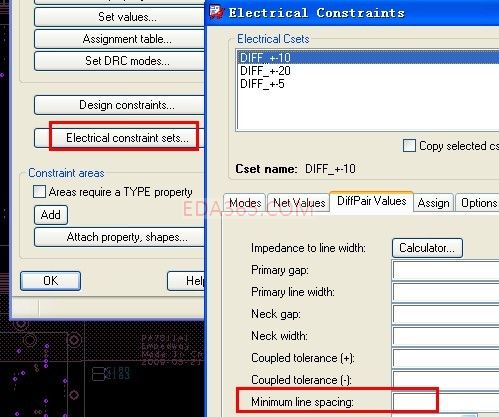

方法三、这里也行:

方法三16.x没了,你找找一、二吧,方法都是想通的。

多谢达人,我去试试,感谢~~~

好像还是不行,无解中。