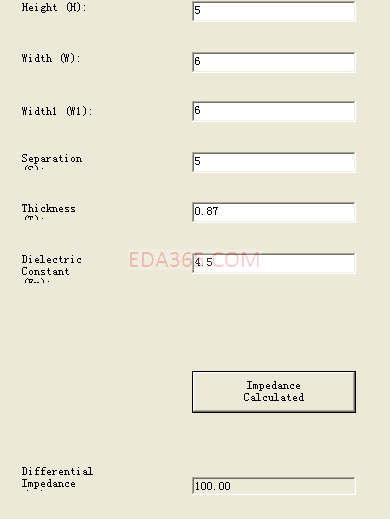

6mil线宽和5mil线距可以叠出100ohm差分阻抗吗?

把叠层等参数发上来

面试官不是神

这样的行否?

请教

xiex ie

可以的,我刚发了一款板子就这样叠的

明白了,谢谢!

能找到这样的板厂叠层吗?你的单线阻抗呢?

应该做不出来!我算了下可以!应该是工艺达不到

我有块这样的板子正要做,请教有板厂可以做到吗

不希望改变线宽线距,但可以调整板厚。能做到吗?

调整板厚要注意参考层的厚度.设备好的公司应该能做出来吧,,我上次就这样做的小厂做不出来,硬要调整线宽.不过你在发板前可以问问板厂.

看你的层叠计算方法,应该是表层微带线,有几个问题你看一下

1:表层铜厚太薄,一般表层都是0.5oz基铜加电镀(要过孔必须电镀),这样完成厚度大约在1.5oz左右,就是1.8mil。而你的厚度只有0.78。

2:线路加工时候会有侧蚀现象,所以W一般要比W1小0.5~1mil,也就是5mil

3:由于组阻焊层的影响,表层走线计算差分阻抗要减小10个欧姆左右。

4:阶电常数不要取的过大,要看办厂的用料,否则工厂计算就没有余量了。最好取4.2~4.3左右(5mil厚度)

这样计算下来阻抗可能就要小很多了,所以差分线的线距还是不要做的太小,否则工厂加工会有困难。

看你的层叠计算方法,应该是表层微带线,有几个问题你看一下

1:表层铜厚太薄,一般表层都是0.5oz基铜加电镀(要过孔必须电镀),这样完成厚度大约在1.5oz左右,就是1.8mil。而你的厚度只有0.78。

2:线路加工时候会有侧蚀现象,所以W一般要比W1小0.5~1mil,也就是5mil

3:由于组阻焊层的影响,表层走线计算差分阻抗要减小10个欧姆左右。

4:阶电常数不要取的过大,要看办厂的用料,否则工厂计算就没有余量了。最好取4.2~4.3左右(5mil厚度)

这样计算下来阻抗可能就要小很多了,所以差分线的线距还是不要做的太小,否则工厂加工会有困难。

转!

1.6MM厚的板的话,差分线外层线宽5MIL,线距7MIL,内层线宽5MIL,线距10MIL可以达到100欧姆的差分阻抗。

单端走线外层7MIL,内层6MIL可以达到50欧姆的阻抗。

叠层如下:

TOP ----------------------------SIGNAL 1.9mil

2116 4.5mil

LAYER2-------------------------- GND 1.2mil

core 8mil

LAYER3-------------------------SIGNAL(主) 1.2mil

2116*2 7.8mil

LAYER4--------------------------- GND 1.2mil

core 14mil

LAYER5--------------------------POWER 1.2mil

2116*2 7.8mil

LAYER6-------------------------SIGNAL(主) 1.2mil

core 8mil

LAYER7--------------------------GND 1.2mil

2116 4.5mil

BOTTOM--------------------------SIGNAL 1.9mil

7630 (PP) 8.0 mil 2116 (PP) 4.1 mil

1018?是1080吧?

他们都是半固化片(PREPREG)的一种, 不同的型号厚度、树脂含量等都不同,1080大约是2.6~2.8MIL, 2116大约是4.5MIL左右。