如何把“器件内的引脚间距”和“器件与器件的间距”设置成不同的值?

时间:10-02

整理:3721RD

点击:

比如:

有一个器件封装,引脚间距0.95mm,中间间隙(Air Gap)0.35mm。

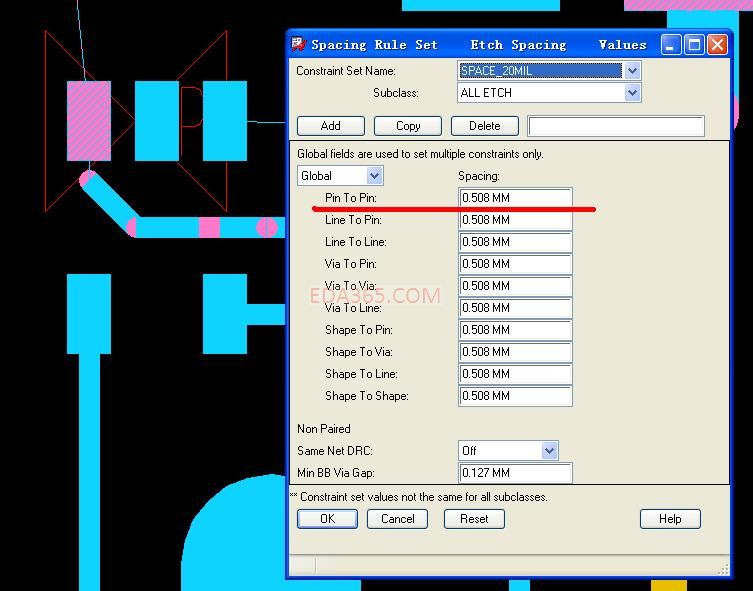

设计规则中电源线与其它走线间距设为0.508mm,那这样报如图DRC错误。

其中设置的Pin to Pin是应该是不仅包括了器件内部的引脚与引脚之间的距离,也包括了器件与器件之间引脚的距离(比如两个0805电阻之间引脚的距离),那我想器件与器件之间的引脚间距至少0.508mm,而不必理睬器件器件内部的引脚距离比0.508mm小,我该如何设置?

不知道大家明白我的问题没有?

有一个器件封装,引脚间距0.95mm,中间间隙(Air Gap)0.35mm。

设计规则中电源线与其它走线间距设为0.508mm,那这样报如图DRC错误。

其中设置的Pin to Pin是应该是不仅包括了器件内部的引脚与引脚之间的距离,也包括了器件与器件之间引脚的距离(比如两个0805电阻之间引脚的距离),那我想器件与器件之间的引脚间距至少0.508mm,而不必理睬器件器件内部的引脚距离比0.508mm小,我该如何设置?

不知道大家明白我的问题没有?

自己的问题自己解决。

把pin to pin设小点儿算了。这可能是最方便的解决方法。

自问自答,自娱自乐,很好很强大。

另:Allegro中的DRC间距全部指的是Air Gap!

也许把器件引脚画个constraint area,另设一个约束,估计也可以,但没有尝试。

其实这问题应该很常见,设置的不适合会报N多恐怖的DRC啊~!

这个方法可行,偶就是这么做的

Edit->Properties

Find:symbols

楼上兄弟给加个属性,这个还没设置过,不太清楚是干什么用的。

但看字面的意思是“元件内相同网络引脚不显示DRC”,是不是这个意思啊?

设了之后封装内的PIN之间就不会报DRC了