一个超难问题,关于设置约束区域的

时间:10-02

整理:3721RD

点击:

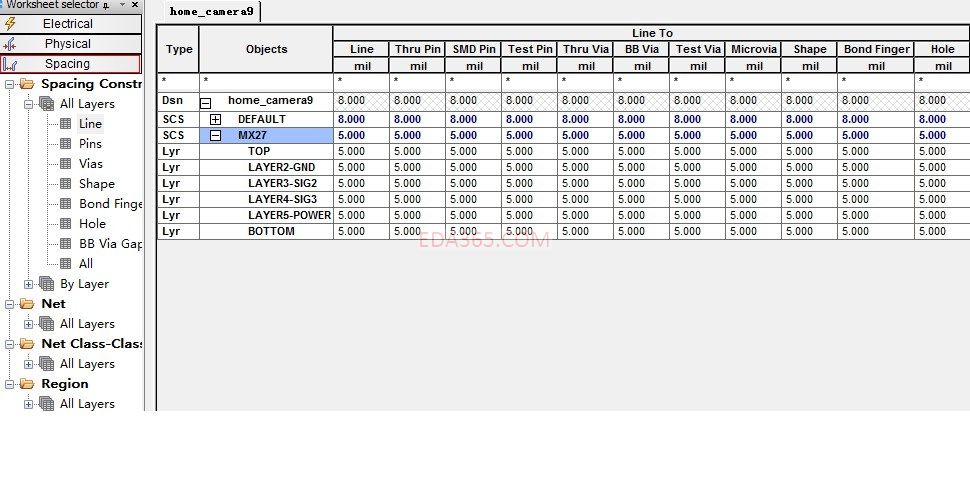

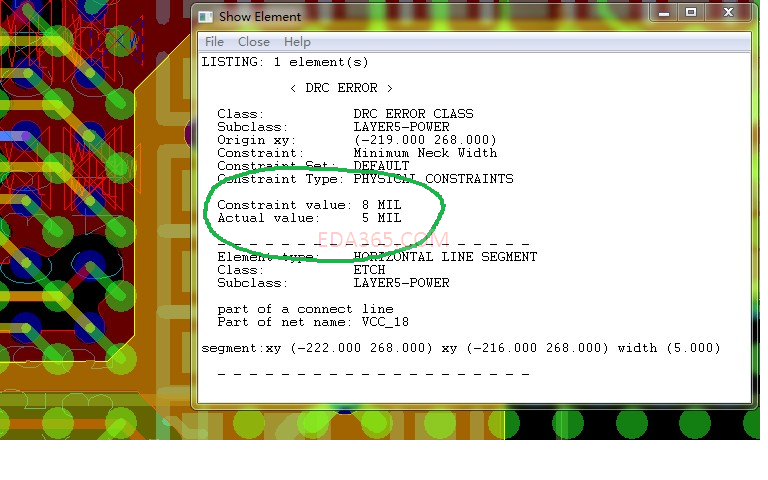

遇到一个问题,设置了一个特殊的Spacing约束区域,设置好后在约束区域内怎么还报错啊?

小编在吗?能给解答下吗?之所以设置一个特殊约束区域,是因为中间一块全是BGA元件,需要比较小的走线间距,而其它区域为了减少制板出问题的概率,则没必要设置这么小的走线间距。谢谢!

还是在用default的设置进行检查啊,是不是要设置规则的优先级?呵呵,我猜的

我也考虑到这问题了,系统还是用default规则来检查的。但怎么能改呢?按理说我要设置了专门的约束区域,系统应该首先承认啊!

Allegro设置RULE我觉得有一个非常重要:比对.很多的RULE需要比对过后才能实现我们想要的状态,16.01往后的版本都需要我们手动的去比对,不象15.51那样跑一下就OK.(可能也有程式,而我不知道了)

在SPACING的REGION里面需要去建立一个REGION-CLASS等等,然后根据需要去选择套用的规则.

(本本坏了,不然可以做个档案看看了)希望对你有帮助!

把区域cope一下,试试

使用的MX27主芯片?做视频监控吗?

楼上的厉害,这都能看出来。

不知道。需要高手来解答,不过帮你顶!

直接画一个Region area,设置相应的rule就可以了

应该先行设置规则,设定允许值。

这个需要慢慢琢磨

我也遇到了这个问题,请教如何解决的!