求救ALLEGRO布局部分元件放不了ALLEGRO界面里

我用的是第一种方法。为什么最后U1,JK1,(T1,T2,T3,T4共用一个PCB封装)。无论自己怎么放,还是放不了ALLEGRO界面里。

之前以为是封装没有做好。于是重新做了JK1/T1的封装。再导入NET。最后。还是老样子

请求大家看看这是什么情况。

看它提示是什么原因先?

他的提示跟放其他元件的提示是一样的,明天上班我上传上来吧

上班了.刚刚又试了一下.还是放不了U1

请看看输入命令栏的报告吧

我有以下三点建议:

1:看一下原理图该封装的管脚的数目是不是和pcb封装的数量一样

2:看一下该器件的pad是否在库中

3:pcb封装名和原理图是否一致

有可能是樓上說的第一點!

如果是5楼说的原因的话,导入网表时就会提示错误了

应该是5楼说的第一点的问题

如果是你PCB封装引脚数比原理图符号引脚数多的话

导网表时只会是warning

如果反过来才会是error

warning是可以忽略的

所以小编会出现这样的问题 log里面有提示pin numbers dont match,check device...

是的.刚刚才发现原理图只有几个PIN.PCB封装它却多了几个PIN.

崩溃.在PADS里面.只有原理图比PCB的脚会多的时候的时候. 才会有问题的呀.

怎么ALLEGRO里面.原理图一定要跟PCB数量一样吗.

这样的话.只能改原理图了吧..

厉害,

还真的是PCB封装引脚数比原理图符号引脚数多

怪不得他们要求我一定要把NC都画上,要不会报错。原来真有。

刚刚又去看错误报告.有很多警告

Spawning... "C:\Cadence\SPB_15.5\tools\capture\pstswp.exe" -pst -d "d:\project\sch\allegro\pdc20090213.dsn" -n "d:\project\sch\allegro\allegro" -c "C:\Cadence\SPB_15.5\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"

#1 Warning [ALG0047] "No_connect" property on Pin "IC1.7" ignored for IC1: SEND, MCU (13.50, 4.00). Connecting pin to net "N16888364".

#2 Warning [ALG0047] "No_connect" property on Pin "IC1.5" ignored for IC1: SEND, MCU (13.50, 4.00). Connecting pin to net "N16888362".

#3 Warning [ALG0047] "No_connect" property on Pin "IC1.11" ignored for IC1: SEND, MCU (13.50, 4.00). Connecting pin to net "N16888046".

#4 Warning [ALG0047] "No_connect" property on Pin "JK1.1" ignored for JK1: SEND, MCU (11.90, 9.20). Connecting pin to net "CAMERA".

SINGLE_NODE_NETS ON

SPLIT_MINIMUM 0

SUPPRESS 20

WARNINGS ON

No error detected

No oversight detected

No warning detected

cpu time 0:01:11

elapsed time 0:00:00

我看了原理图.它们都是连接在一起的.我想只要导网络不删除网络就可以了吧.

现在元件全部可以放入到ALLEGRO里面了. 那这些警告可以忽略吧

下一布就是布局了.

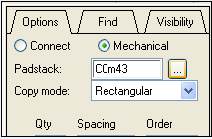

也可以在画封装的时候把多余的PIN做如下设置为Mechanical

就不会出现错误了

高手呀.原来把多的PIN改成机械的而非元件.就可以避免了

谢谢.受教了..