I want to design a voltage-controlled ring oscillator

I want to design a voltage-controlled ring oscillator, a simple, low-speed, wide-tuning oscillator, anyone can offer any help?

thanks in advance!

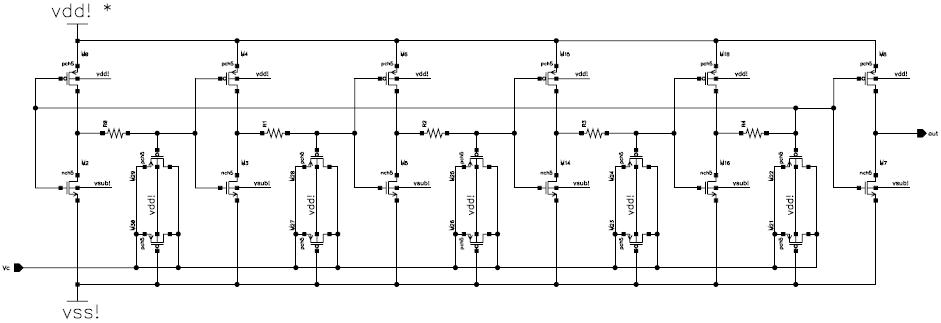

check this , the transistors with the DC input are the transsitors used in control

this work , as u change the DC voltage uchange the current the upper inverter so the delay of the inverter change , so the frequency of oscillation will change as well

khouly

Dear khouly

thank you very much

your circuit is good, and i will try it

i have already design a ring oscillator circuit, it work well in simulation

i'm glad to get your suggestion or advice

Dear gingerjiang

i have check ur circuit , it is good , and the nice thing about it , that u change the delay of the inverter by changing the load capacitance by the varactors used

mine is by changeing the current ,

i donot know which one will give u wide tuning range , u have to check it by simulatin , also u have to check the phase noise performance of each

and then decide which one will be more suitble ,

also u have to check how to add a voltage to current converter , to the current controlled ring oscillator

khouly

dear khouly

i have simulated these two circuits, and now i use your circuit.

i find that your circuit's tuning range is larger, while mine's control voltage is disturbed by clock feedthrough, meanwhile isn't robust by process variation.

thank you very much

you said that i should check the phase noise performance, i'm beginner. would you like to introduce me how to simulate it?

it depends on which tool u will use

ADS which is based on HB "Harmonic Balance" or Cadence which use PSS "Periodic Steady State"

if ADS i can help you , if cadence check this appnote by cadence it is very good

http://www.cadence.com/community/vir...F_VCO533AN.pdf

khouly

i have some question, when you simulate the ring oscillator, what is its phase noise and the offset frequency?, what is the Phase noise typically in a ring oscillator?

thanks

about the phase noise and frequency offset , u should specify it , coz u measure it according to a standard ,

about the typical valuse i don't have an accurate number but generally it will be for sure worth than LC oscillator

khouly

i just want to know worth to what extent , i know it may be much worth but for example at 3 MHz offset , phase noise typically ?

thanks

dear khouly

i use cadence, and i have download the document you provide, and i will try it

thanks again

ok , simulate it and we will see

and what about ur PLL , did u tried to minimize the jetter

khouly

i use cadence to simulate the ring oscillator, but failed

i don't know the cause, maybe need the special rf model for MOS transistors?

so i want to use ADS, would you like help me?

sure

mainly to do oscillator analysis in ads use transient or HB analysis

which version of ads do u use ?

check the manual of ADS about HB smulation , u will find there a good example

khouly

hi khouly

i use cadence to simulate the ring oscillator, and it is successful

thank you anyway

i found the noise of ring oscillator is large, how can i reduce it? which methods are there generally?

typically in Ring oscillator the phase noise is larger than LC oscillators

but i donot know how to minimize the phase noise of ring oscillator

may be one of the experts help us to do so

khouly

voltage design controlled 相关文章:

- Induced voltages on transmission line by plane wave in HFSS

- Klystron output voltage, cavity field strength

- Negative voltage needed in K-band

- How to set the bias voltage of the BJT in Gilbert mixer

- is DC voltage gain not an important issue to consider in LNA designing?

- Power (Voltage / Current) inducted in rectangle antenna.