请教一下ahdlLib里头运放代码中的cont是什么

`include "constants.h"

// $Date: 1997/08/28 05:45:21 $

// $Revision: 1.1 $

//

//

// Based on the OVI Verilog-A Language Reference Manual, version 1.0 1996

//

//

`define PI

3.14159265358979323846264338327950288419716939937511

//--------------------

// opamp

//

// -operational amplifier

//

// vin_p,vin_n:

differential input voltage [V,A]

// vout:

output voltage [V,A]

// vref:

reference voltage [V,A]

// vspply_p:

positive supply voltage [V,A]

// vspply_n:

negative supply voltage [V,A]

//

// INSTANCE parameters

//gain= gain []

//freq_unitygain = unity gain frequency [Hz]

//rin= input resistance [Ohms]

//vin_offset= input offset voltage referred to negative [V]

//ibias= input current [A]

//iin_max= maximum current [A]

//slew_rate= slew rate [A/F]

//rout= output resistance [Ohms]

//vsoft= soft output limiting value [V]

//

// MODEL parameters

//{none}

//

module opamp(vout, vref, vin_p, vin_n, vspply_p, vspply_n);

input vref, vspply_p, vspply_n;

inout vout, vin_p, vin_n;

electrical vout, vref, vin_p, vin_n, vspply_p, vspply_n;

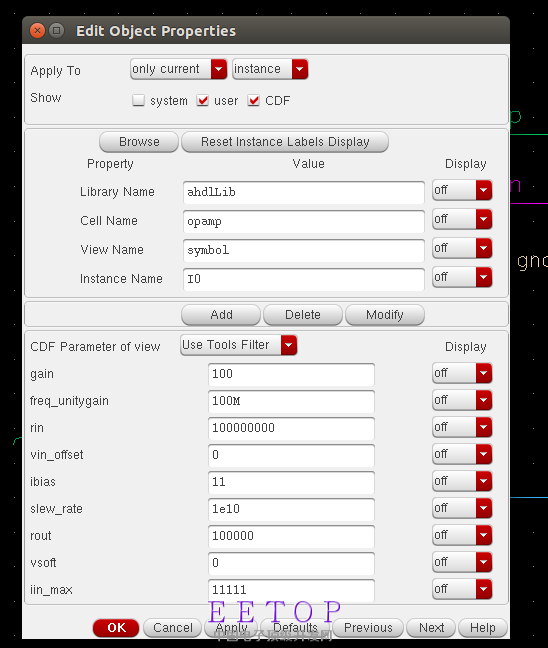

parameter real gain = 835e3;

parameter real freq_unitygain= 1.0e6;

parameter real rin = 1e6;

parameter real vin_offset = 0.0;

parameter real ibias = 0.0;

parameter real iin_max = 100e-6;

parameter real slew_rate = 0.5e6;

parameter real rout = 80;

parameter real vsoft = 0.5;

real c1;

real gm_nom;

real r1;

real vmax_in;

real vin_val;

electrical cout;

analog begin

@ ( initial_step or initial_step("dc") ) begin

c1 = iin_max/(slew_rate);

gm_nom = 2 * `PI * freq_unitygain * c1;

r1 = gain/gm_nom;

vmax_in = iin_max/gm_nom;

end

vin_val = V(vin_p,vin_n) + vin_offset;

//

// Input stage.

//

I(vin_p, vin_n) <+ (V(vin_p, vin_n) + vin_offset)/ rin;

I(vref, vin_p) <+ ibias;

I(vref, vin_n) <+ ibias;

//

// GM stage with slewing

//

I(vref, cout) <+ V(vref, cout)/100e6;

if (vin_val > vmax_in)

I(vref, cout) <+ iin_max;

else if (vin_val < -vmax_in)

I(vref, cout) <+ -iin_max;

else

I(vref, cout) <+ gm_nom*vin_val ;

//

// Dominant Pole.

//

I(cout, vref) <+ ddt(c1*V(cout, vref));

I(cout, vref) <+ V(cout, vref)/r1;

//

// Output Stage.

//

I(vref, vout) <+ V(cout, vref)/rout;

I(vout, vref) <+ V(vout, vref)/rout;

//

// Soft Output Limiting.

//

if (V(vout) > (V(vspply_p) - vsoft))

I(cout, vref) <+ gm_nom*(V(vout, vspply_p)+vsoft);

else if (V(vout) < (V(vspply_n) + vsoft))

I(cout, vref) <+ gm_nom*(V(vout, vspply_n)-vsoft);

end

endmodule

看了好几遍直接从electrical cout; 就到电流电压节点公式了, 有木有老师说一下这个cont是干啥的 ,顺便问一下

I(vin_p, vin_n) <+ (V(vin_p, vin_n) + vin_offset)/ rin;

I(vref, vin_p) <+ ibias;

I(vref, vin_n) <+ ibias;

这个ibias是干啥的呢,是在搞不懂啊

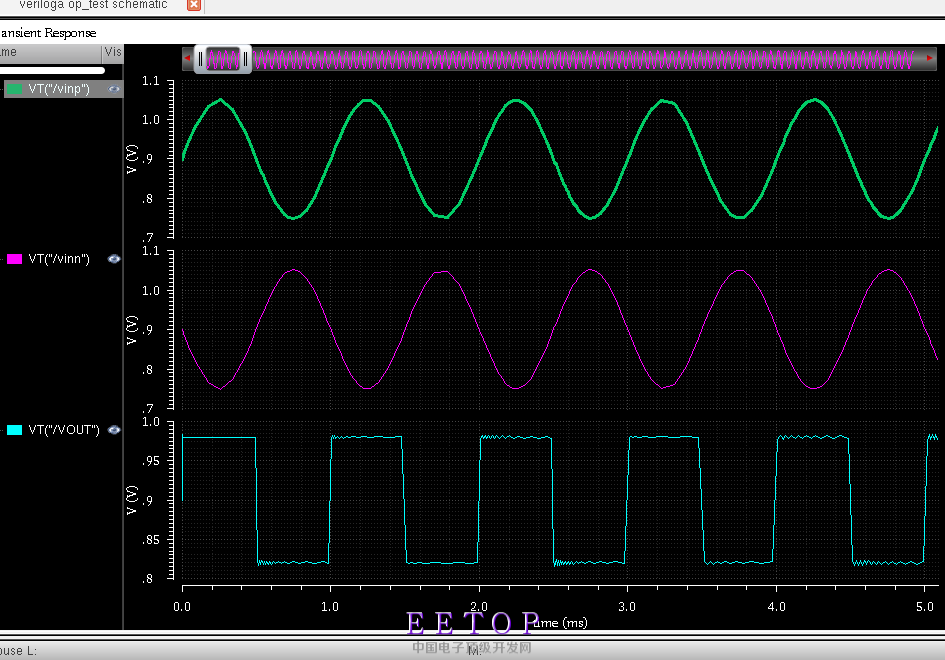

输入信号1k,振幅差分300mV的正弦波,电源电压1.8,运放GBW100M,低频增益40db,然后输出是个方波?在970-830mV之间什么鬼

提问中的cont应该是cout吧。

cout是GM stage中的一个电学节点,是对输入级之后的V 到 I转换的GM的建模。

ibias模拟的是双极型放大器输入端的偏置电流,对于CMOS技术没有意义。但是别忘了这个opamp模型不是针对某一个工艺的,所以双极型的模型也在里面了。

后面提问的仿真结果问题,我另外再看看 ...

对于仿真结果的回答:

1) 40的B,100倍的增益早就超出1.8V电源电压范围了,你看到的波形其实就是数学处理的结果,不是真实的电路响应

2) 将增益值改到比较小的数值,比如3倍或者4倍,你就会看到你看得懂的波形了

3) 你这个波形浏览器是什么?看起来像数字电路的波形浏览器,不能用wavescan试一下吗?

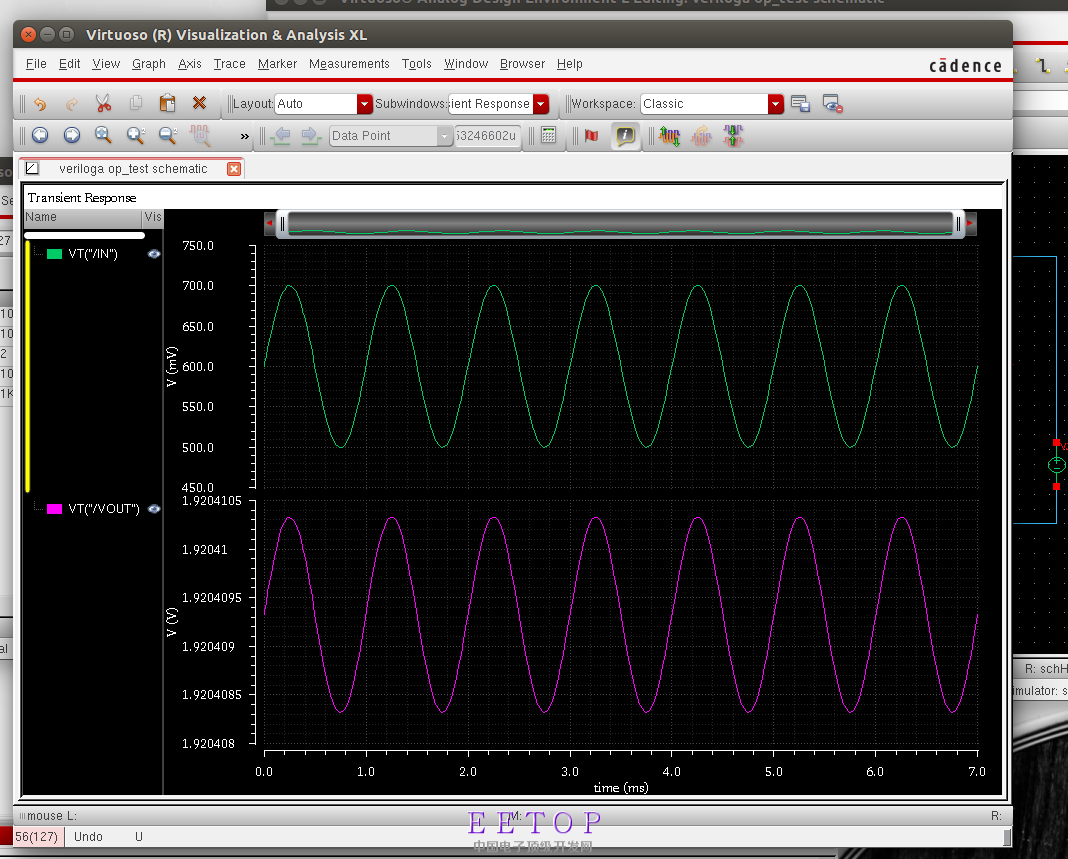

这是将增益设置到2.5倍的仿真结果,在输入幅度300mV条件下,输出单端幅度是750mV.

感谢老师回复1,那个是cout 昨天手机打字打了一堆错别字

2,那个是ade L spectre plot出来的图 不过是在虚拟机ubuntu的ic615的软件,可能跟红帽的看起来有区别。

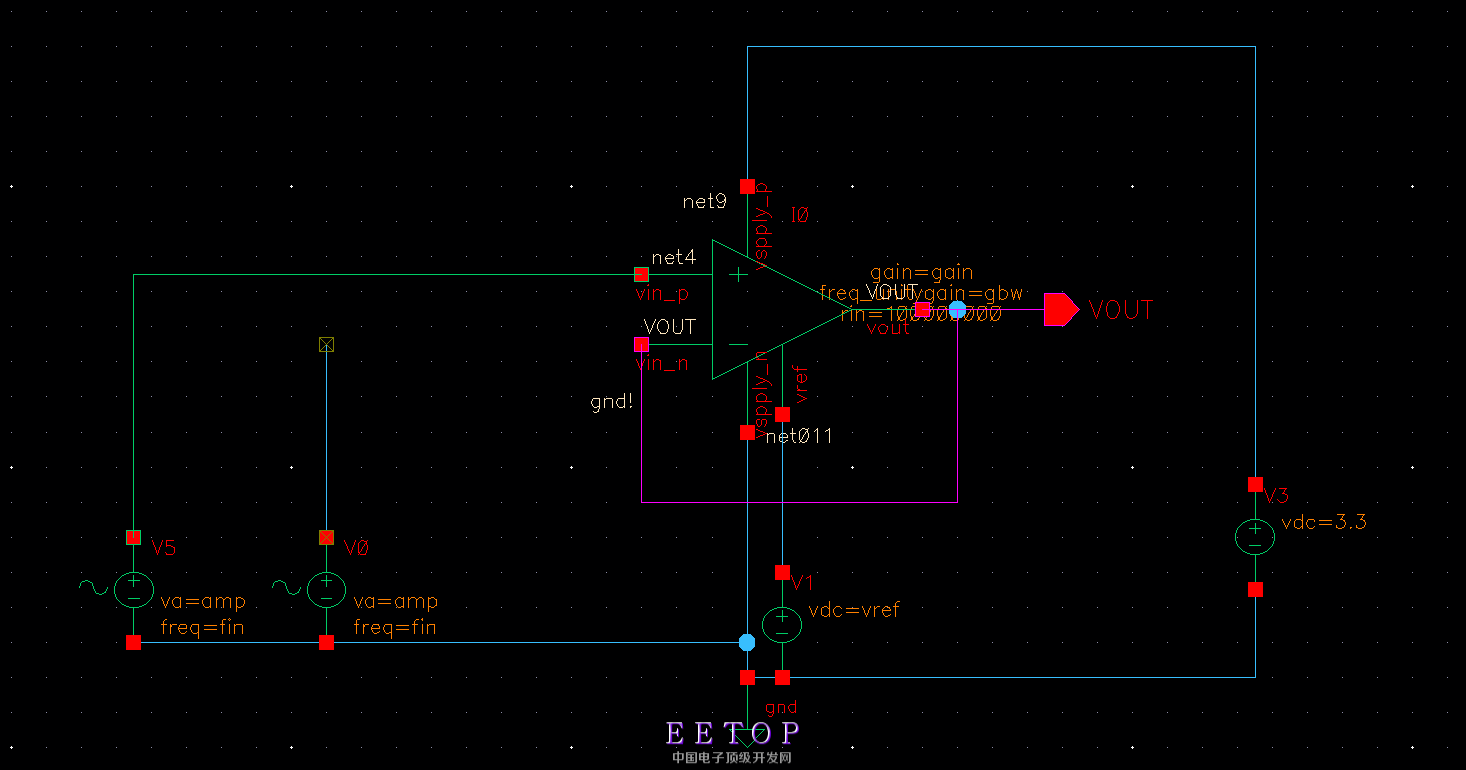

3,根据老师的说法,我把增益调低,可以出来正常的波形,除了发现增益的问题,我发现增益与gbw都不能太大,在接成闭环的情况下,gbw设置过大导致输出又有很多问题,不是输出是方波就是输出波形幅度很小,如图是我接成负反馈增益变的很小的情况,当我gbw设的很大时比如100M,输出是方波,麻烦老师没事的话有时间分析一下,感觉这个代码没有考虑cmos工艺的情况

4,有一个图是我觉得这个代码设计的运放的节点的思路。

ps,其实我想设计一个理想的运放用在pipelineADC上,但是感觉这个运放限制条件太多也不明确

上图输出增益过小的情况不是方波这个仿真时出现方波的情况而且波形也很小,反正我已经晕了

回答你6#提出的问题,为什么输出波形这么小。

你顺着代码把自己输入的参数代入进去,就知道你的输出幅度受限于vmax_in了,这确实是由于你的gbw和slew_rate数值设置造成的。而且这个仿真里面的很多模型参数设置都不合理,仅仅是mathematically right, 没有实际的电路意义。